# Specification Analysis for System-Level Power-Aware ASIC Design

**Doctoral Thesis**

David Ariel Lemma

Adviser: Prof. Dr. Rolf Drechsler

# Specification Analysis for System-Level Power-Aware ASIC Design

**David Ariel Lemma**

A Dissertation Submitted in Partial Fulfillment of the Requirements for the Degree of Doctor of Engineering

- Dr.-Ing. -

Date of doctoral colloquium: 21.09.2021

1. Reviewer Prof. Dr. Rolf Drechsler

Universität Bremen

2. Reviewer Prof. Dr. Oliver Keszöcze

Friedrich-Alexander-Universität

Erlangen-Nürnberg

#### **Abstract**

The field of *Electronic Design Automation* (EDA) is a growing field whose growth is fueled, among many factors, by the ever increasing number of Application Specific Integrated Circuits (ASIC) that are required by several digital systems. Amidst the current explosion in the design and production of Internet of Things (IoT) (typically battery powered devices), the need for power-aware design has come to reach critical importance. The need for a holistic view (power-aware) of the implications and challenges brought forth by the need to curb and properly manage power consumption power has revealed a need for the EDA field to explore system-level top-down based methodologies. As a response to the needs, this research document presents two frameworks based on specification analysis at the system-level in order to address the holistic view of power-aware design. One of the frameworks focuses on system-level specifications written in natural language (ie. English), whereas the other focuses on system-level specifications written in a technical language (ie. SystemC). The frameworks are shown to be able to analyze these types of system-level specifications as a means to aid designers in power-aware ASIC design at the system level. These frameworks encapsulate the contributions of this thesis, which are defined by the proper devising of analytical rules to parse the systemlevel specification so as to extract the basic underlying Power Management Strategy (PMS) laid out of by the specification under analysis. Use cases that show the effectiveness of the frameworks in aiding designers include typical ASIC elements such as a bus, a port processor, encoders and a processor centric programmable System-on-Chip (SoC), all of them also typical components of IoT devices. The research document ends with a conclusion both summarizing the work and pointing to possible future extensions to the frameworks and general research lines that are possibles avenues for future developments in the field of specification analysis for power-aware system-level ASIC design.

### Acknowledgements

I would like to extend my gratitude to many people who have contributed to the completion of my doctoral journey with this doctoral thesis.

Firstly, I would like to express my thankfulness to Prof. Dr. Rolf Drechsler for the opportunity to do research work in AGRA, a group of very warm people and strong research output. It has been an experience that I shall never forget.

Secondly, my sincere appreciation goes to Prof. Dr-Ing Daniel Große and Dr. Mehran Goli. Simply put, without their assistance in research, co-authorship of papers and general advice, this thesis would not have been possible.

Thirdly, I would like to extend my greeting and well wishes to the entire membership of AGRA and to the members of CPS with whom I've shared more than 4 years of daily work.

Lastly, but certainly not least, I owe an immense debt of gratitude to my parents. Without their constant care, love and advice, this whole experience would have been duller and significantly less enjoyable.

## Contents

| 1  | Intr  | oduction and Motivation                                         | 5  |

|----|-------|-----------------------------------------------------------------|----|

|    | 1.1   | Introduction                                                    | 5  |

|    | 1.2   | Motivation                                                      | 7  |

|    | 1.3   | Contributions                                                   | 8  |

|    | 1.4   | Thesis Structure                                                | 10 |

| 2  | Pow   | er-Aware Design: Implications, Challenges and Responses         | 12 |

|    | 2.1   | Preface                                                         | 12 |

|    | 2.2   | Implications                                                    | 15 |

|    | 2.3   | Challenges                                                      | 17 |

|    | 2.4   | Responses                                                       | 20 |

|    |       | 2.4.1 Power Management Unit (PMU)                               | 20 |

|    |       | 2.4.1.1 Power Domain                                            | 24 |

|    |       | 2.4.1.2 Control Signal                                          | 24 |

|    |       | 2.4.1.3 Power Mode                                              | 24 |

|    |       | 2.4.1.4 Power Domains, Control Signals and Power Modes          |    |

|    |       | and the PMU                                                     | 25 |

|    |       | 2.4.1.4.1 Power Domain Partitioning                             | 25 |

|    |       | 2.4.1.4.2 Setting of Control Signals and Power Modes            | 26 |

| Pa | rt I: | Natural Language Specifications                                 | 30 |

| 3  | Nati  | ıral Language: Preliminaries, Relevant Work and Response Frame- |    |

|    | wor   | k                                                               | 31 |

|    | 3.1   | Preliminaries                                                   | 31 |

|    |       | 3.1.1 Power-aware Interpretation                                | 36 |

|    | 3.2   | Relevant Work                                                   | 37 |

|    | 3.3   | Response Framework                                              | 39 |

|    |       | 3.3.1 Architectural Overview                                    | 39 |

|    |       | 3.3.2 The Stages of the Response Framework                      | 41 |

|    |       | 3 3 2 1 The Information Extraction Stage                        | 42 |

|    |        |          | 3          | .3.2.1.1   | Natural Language Processing and Universal |    |

|----|--------|----------|------------|------------|-------------------------------------------|----|

|    |        |          |            |            | Dependencies                              | 43 |

|    |        |          | 3          | .3.2.1.2   | From Universal Dependencies to Triples    | 46 |

|    |        |          | 3.3.2.2    | The Rea    | asoning Stage                             | 48 |

|    |        |          | 3.3.2.3    | The Ou     | tputs                                     | 52 |

|    |        |          | 3.3.2.4    | Limitati   | ons of the Response Framework             | 53 |

|    | 3.4    | Conclu   | ding Ren   | narks      |                                           | 55 |

| 4  | App    | lication | of the r   | esponse    | framework                                 | 56 |

|    | 4.1    | ASIC D   | esigns fr  | om Natu    | ral Language                              | 56 |

|    | 4.2    | The LZ   | W Encoc    | ler        |                                           | 58 |

|    |        | 4.2.1    | Extraction | ng the Tr  | iples                                     | 60 |

|    |        | 4.2.2    | Rules an   | ıd Reasor  | ning                                      | 62 |

|    |        | 4.2.3    | Power D    | omain Pa   | artitioning Scheme and Power Modes        | 63 |

|    |        | 4.2.4    | Validatio  | on of the  | e Power Domain Partitioning Scheme and    |    |

|    |        |          | Power M    | Iodes      |                                           | 64 |

|    | 4.3    | The HI   | MI Port    | Processo   | r                                         | 66 |

|    |        | 4.3.1    | Extraction | ng the Tr  | iples                                     | 67 |

|    |        | 4.3.2    | Rules an   | ıd Reasor  | ning                                      | 69 |

|    |        | 4.3.3    | Power D    | omain Pa   | artitioning Scheme and Power Modes        | 70 |

|    |        | 4.3.4    | Validatio  | on of the  | e Power Domain Partitioning Scheme and    |    |

|    |        |          | Power M    | Iodes      |                                           | 7  |

|    | 4.4    | Conclu   | ding Rer   | narks      |                                           | 73 |

| Pa | rt II: | Technic  | al Lang    | uage Spe   | ecifications                              | 75 |

| 5  | Tecl   | nnical L | anguag     | e: Preli   | minaries, Relevant Work and Response      |    |

|    | Frai   | nework   |            |            |                                           | 76 |

|    | 5.1    | Prelimi  | naries .   |            |                                           | 76 |

|    | 5.2    | Relevai  | nt Work    |            |                                           | 82 |

|    | 5.3    | Respon   | se Fram    | ework      |                                           | 84 |

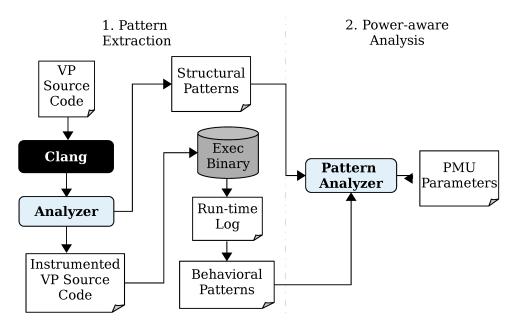

|    |        | 5.3.1    | The Firs   | t Phase: 1 | Pattern Extraction                        | 84 |

|    |        | 5.3.2    | The Sec    | ond Phas   | e: Power-aware Analysis                   | 88 |

|    |        | 5.3.3    | Limitatio  | ons of the | e Response Framework                      | 92 |

|    | 5.4    | Conclu   | ding Ren   | narks      |                                           | 93 |

| 6  | App    | lication | of the P   | Response   | Framework                                 | 95 |

|    | 6.1    | ASIC D   | esigns fr  | om Techi   | nical Language                            | 95 |

|    | 6.2    | The Ha   | mming l    | Encoders   | and Other Benchmarks                      | 96 |

|    | 6.3    | A Large  | er TLM V   | P Use Ca   | se                                        | 99 |

|    | 6.4   | Concluding Remarks | 105 |

|----|-------|--------------------|-----|

| 7  | Con   | clusion            | 106 |

|    | 7.1   | Summary            | 106 |

|    | 7.2   | Future Work        | 108 |

| Βi | bliog | raphy              | 110 |

# List of Figures

| 2.1 | Design Level Ladder and its Impact on Power from [25]                | 16 |

|-----|----------------------------------------------------------------------|----|

| 2.2 | Design Levels and Design Tasks Associated with Them based on [30] .  | 17 |

| 2.3 | Frequent Power management Techniques from [31]                       | 18 |

| 2.4 | Gajski-Kuhn Y Diagram                                                | 22 |

| 2.5 | Example of a Power Domain Partitioning Scheme from [35]              | 26 |

| 2.6 | An IoT Device's Power Domain Partitioning Scheme from [39]           | 28 |

| 2.7 | An IoT Device's Power Modes and Power States from [39]               | 28 |

| 3.1 | Flow/Block diagram for the FIR Filter                                | 35 |

| 3.2 | Architecture of the Expert System                                    | 40 |

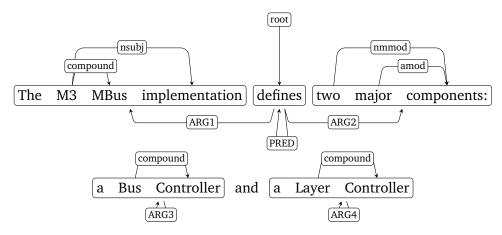

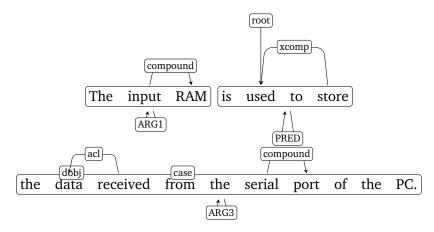

| 3.3 | Example of a Predicate-Argument Extraction based on UD               | 44 |

| 3.4 | Output of a Predicate-Argument Tool for Part of the Running Case     | 46 |

| 3.5 | Domain Specific Triples from Part of the Selected Input              | 47 |

| 3.6 | Another Domain Specific Triple from Part of the Selected Input       | 50 |

| 3.7 | Excerpt of the Rules                                                 | 51 |

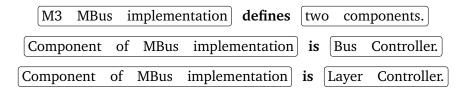

| 4.1 | Block Level Diagram of LZW Encoder based on[71]                      | 58 |

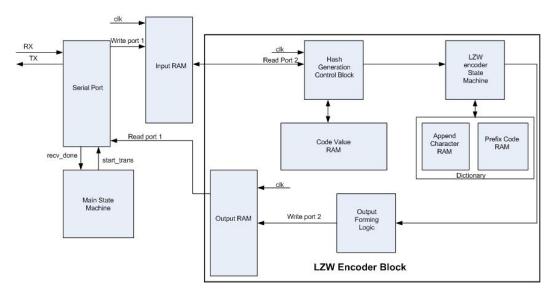

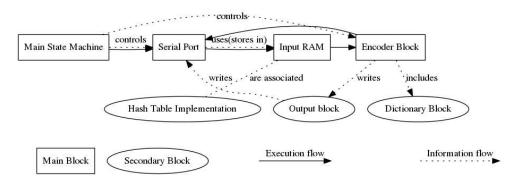

| 4.2 | LZW Encoder Semantic Map                                             | 61 |

| 4.3 | Simplified Predicate-Argument Output for Part of the LZW Encoder     |    |

|     | Specification                                                        | 62 |

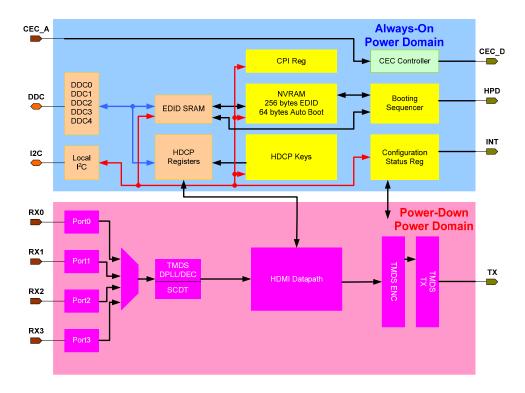

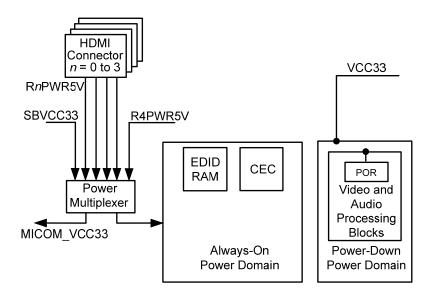

| 4.4 | The Basic Architecture of the HDMI Port Processor from [74]          | 67 |

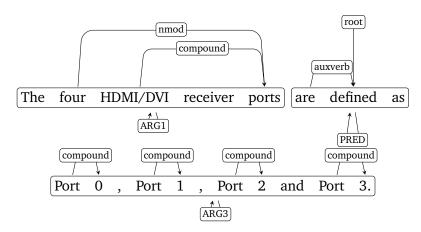

| 4.5 | Simplified Predicate-Argument Output for Part of the HDMI Port Pro-  | 60 |

|     | cessor Specification                                                 | 68 |

| 4.6 | Power Modes of the HDMI Port Processor from [74]                     | 72 |

| 4.7 | Simplified Power Architecture of the HDMI Port Processor from [74] . | 73 |

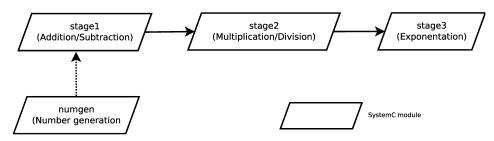

| 5.1 | Part of Pipe Design Implemented in SystemC                           | 78 |

| 5.2 | Architecture of the Pipe Example                                     | 78 |

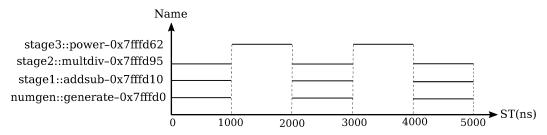

| 5.3 | Part the Pipe's Activity Profile                                     | 79 |

| 5.4 | Alternative Form of the Activity Profile of the Pipe Example         | 79 |

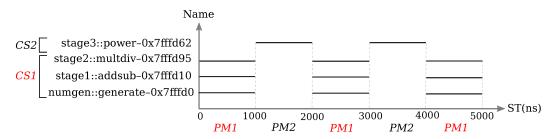

| 5.5 | Control Signals and Power Modes for the Pipe Example                 | 81 |

| 5.6 | The Design Understanding Approach                                    | 82 |

| 5.7  | Overview of the Response Framework                                   | 84  |

|------|----------------------------------------------------------------------|-----|

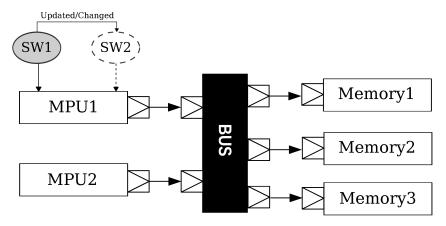

| 5.8  | The Architecture of the Motivating Example                           | 85  |

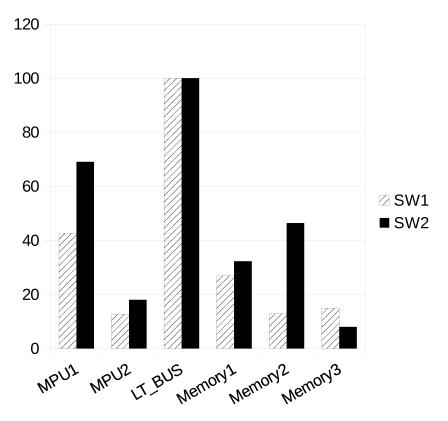

| 5.9  | Activity Percentage of the LT_BUS VP modules for Different Workloads | 86  |

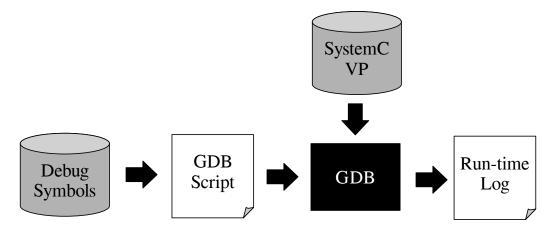

| 5.10 | Part of the Instrumented Source Code of the VP                       | 88  |

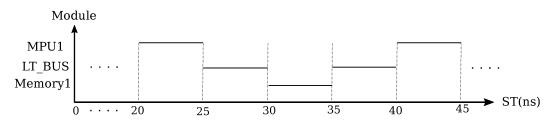

| 5.11 | A Part of the Run-time Log of the VP                                 | 89  |

| 5.12 | A Part of the Activity Pattern of the LT_BUS VP Modules              | 89  |

| 5.13 | Part of a Basic PMU for the LT_BUS VP                                | 91  |

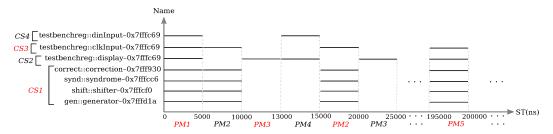

| 6.1  | Part of the Activity Profile for Hamming-seq                         | 97  |

| 6.2  | Part of the Activity Profile for Hamming-comb                        | 98  |

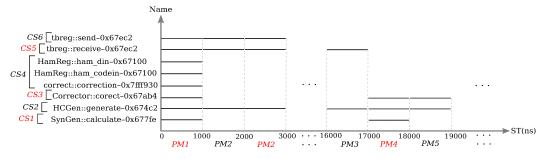

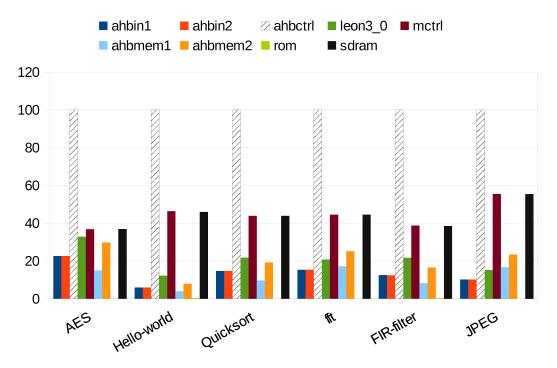

| 6.3  | Activity Percentage of the VP modules for the Different Softwares    | 101 |

## List of Tables

| 2.1 | Some Power Management Techniques and Their Impact               | 19  |

|-----|-----------------------------------------------------------------|-----|

| 3.1 | Entity Extraction                                               | 34  |

| 3.2 | Relationship Extraction                                         | 34  |

| 3.3 | Condensed Tabular Format for the FIR Filter                     | 35  |

| 3.4 | Scores Validating the Approach                                  | 48  |

| 3.5 | Control Signals and Power Modes for the MBus Device             | 53  |

| 4.1 | Precision and Recall within the LZW Encoder Use Case            | 62  |

| 4.2 | Comparison Between Suggested PD Partitioning Scheme and Single  |     |

|     | Domain Scheme for the LZW Encoder                               | 65  |

| 4.3 | Precision and Recall within the HDMI Port Processor Use Case    | 69  |

| 6.1 | Power Parameters for the Alternative Hamming Encoders           | 98  |

| 6.2 | The Response Framework for other Benchmark VP                   | 99  |

| 6.3 | Activity percentage of the modules for the JPEG software        | 102 |

| 6.4 | Activity Percentage of the Modules for the AES Software         | 102 |

| 6.5 | PMU Validation for the Different Scenarios for the SocRocket VP | 103 |

Introduction and Motivation

In design, one of the most difficult activities is to get the specifications right [1]

— **Donald A. Norman** (Professor. Usability engineering and design expert)

#### 1.1 Introduction

Much has transpired since the origins of the *Integrated Circuit* (IC) design industry. 50 years after Gordon Moore first famously observed and proposed the "law" that bears his name, explaining how the number of transistors doubles every year, the IC industry has further developed following the upsurge in the demand for the highest processing power in the smallest possible package. What began in the late 1940s as a way to combine discrete electronic components to produce amplification devices, took a far more generic turn when Jack Kilby showed a working monolithic integrated circuit at the end of the 1950s [2]. While trying to find a way to improve the reliability of the interconnected modules made of discrete components (thereby offering a way to solve the so called "Tyranny of numbers"), Jack Kilby ushered an era in which the electronic circuits grew in complexity, reliability and performance and decreased in size and price[3].

Onto the 1960s and 1970s, the applications of the IC products grew, as their design and manufacturing costs diminished. The evolution of the IC design industry in these decades, also led to the emergence, development and consolidation of the *Electronic Design Automation* (EDA) field, whose techniques and tools supported the ever increasing rate of development. The automation, which began with tools for placement and routing (that is to say, mainly layout tasks), took a massive leap forward in the 1980s, when the number of integrated components in ICs boomed into the hundreds of thousands. Indeed, by the early 1980s, the relatively artisanal way in which IC design had been conducted for the previous two decades, had been

transformed by systematization, spearheaded by the work of pioneers such as Carver Mead and Lynn Conway [4].

As the complexity of IC products was increasing, the EDA industry found itself needing to address an equally increasing number of recurring concerns in the design flow. Many of these concerns were no longer only associated with the layout tasks that had been the object of most of the automation techniques being developed thus far [5]. As the IC design industry moved away from focusing solely on the placement and routing phases of a design, ad-hoc design languages became the preferred way to deal with challenges brought up by the need for verification (assurance of compliance of the design with an specification) and validation (assurance of addressing the need that the design is supposed to meet) [6].

The main companies in the EDA industry became closely acquainted with the use of simulation methods as a viable approach to addressing the demands and requirements of an industry with ever expanding fields of application. What had first started as transistor and logic simulation, incorporated functional simulation, where the increasing need for architectural verification was more appropriately met [7]. Even before that time, the IC design industry had also begun to eye and behold tools and techniques of formal verification (such as model checking and temporal logics) as a more suitable way to address the stringent safety and security requirements of some industries in which ICs were being deployed (as become the case with the aerospace and defense industries).

By the 1980s, the IC industry had been the main driving force behind inherently programmable microprocessors and other general purpose highly configurable computing platforms, which the public had begun to realize were at the core of their digital electronic devices. However, in addition to enabling the design of highly complex comprehensive digital information processing circuits, the EDA community (now a blossoming industry of its own), also enabled the development of more specialized ICs, which became known under the moniker *Application Specific Integrated Circuit* (ASIC). The ASIC world benefited immensely from the creation of *Hardware Description Languages* (HDL), for this mirrored the flexibility of platform independent high-level software programming languages, thereby allowing designers to think of their circuits in increasingly more abstract terms [8] [9].

The creation of HDLs led to a shift away from the transistor and logical levels into the *Register Transfer Level* (RTL), which better suited the design flow from a top-down perspective. The Register Transfer Level not only allowed for a fairly common physical synthesis agnostic platform (as per abstracting away the design from the choice of the underlying transistor and gate technology), but also allowed for a way

to design an IC from a more architectural point of view [10]. Such a point of view led to more system-wide approaches to the validation and verification challenges. Further expansion of the integration of ICs (many of them ASICs) to create full fledged digital *System on Chips* (SoCs) unveiled a pressing need for system-level approaches to address not only validation and verification, but also requirements that were themselves at a system level [11].

The emergence of SoCs (fueled by the need for self contained digital systems) meant that many ASICs turned into *Application Specific Standard Products* (ASSP) [12]. These products were and continue to be, ICs performing specialized standardized tasks typically present in many SoCs (such as buses or encoders/decoders). The specialized and standardized nature of these ICs is typically underlined by elements of their design such as an archetypal architecture. Furthermore, such a characteristic architecture of an ASSP is the natural byproduct of a detailed specification that the design has followed. The necessity of following and conforming to a specification (essentially a set of requirements to comply with) is at the core of the design of these ICs.

#### 1.2 Motivation

Regardless of whether the IC is an ASSP or an ASIC, following and conforming to a specification is paramount. However, as crucial as this precept is in the design flow for any IC, usually the task associated with complying with a specification are quite demanding. The main difficulties are almost always associated with the ambiguities and the extent of the specification. Specifications are rarely of a formal nature (ie. described in a logical formulation), but are instead typically produced in a natural language (ie. English) or in a technical language (ie. a HDL), which captures requirements in more generic concepts. What is more, specifications are the starting point of almost all top down design flows, in which the architectural decisions are taken in early stages [13].

By beginning of the 21st century, technical standards (that is to say, standardized specifications) had grown to cover most, if not all, of the functional concerns related to any ASIC (or ASSP). Verification and validation of the functional requirements had escalated to system level, beyond RTL, in an effort to reduce the iteration cycle required by successive refinements to fulfill the requirements. In these system levels (such as for instance, the *Electronic System Level* (ESL), which is known for the presence of Virtual Prototypes, the *SystemC* technical language [14]) and the

*Transaction Level Modeling* (TLM) methodology [15], the EDA community has strived to ensure reliability in functionality by expanding the use of formal methods and by extending coverage metrics from lower levels of abstraction.

Also by the turn of the millennium, it became discernible that functional requirements were no longer the only sine qua non requirements stemming from specifications. Security, safety and power/energy consumption concerns had risen to rival the sense of priority accorded to functionality, to the point that it had become increasingly impossible to design an IC with only functionality in mind. Indeed, if the prototype for an IC did not meet the security provisions or the power or energy budget, the prototype was to be rejected. Such a heightened importance of non functional requirements, meant that top down design flows were then in need of some changes to reflect such an evolution [16].

While the importance of security and safety in ICs (especially so regarding data protection) is unquestionable, the evolution of the design flow to address power/energy consumption concerns has shown itself to be a top priority. From the transistor level up to a system-level, many of the innovations introduced to deal with the power/energy concerns, have been the result of wide ranging research leading to the concept of power-aware design. With the advent of the *Internet of Things* (IoT), in which ASICs play a central role, these innovations that have brought up power-aware design are shaping up a renovated ASIC design flow [17]. Not unlike the functionality focused design flows, the focus of power aware design techniques has shifted towards system-level architectural decision making. Owing to such a shift, and going beyond the reach of traditional HDLs designed to implement existing designs, specification analysis (often the first step in top down design flows) is becoming a focus area in the coming years [18].

#### 1.3 Contributions

The contributions of this doctoral thesis are centered on addressing some of the challenges of system-level power-aware ASIC design via focus on specification analysis, for both specifications in natural and technical language [19] [20]. For most intents and purposes, the intention is to help usher a new stage in the revamping of top down ASIC design flows. In such a new stage, specifications written in natural/technical languages are considered the foundational design documents at the system-level. As such, specifications (whether technical standards or functional

descriptions) are the main source of information for power -aware decision making, significantly integrating functionality and power/energy consumption concerns.

This document presents two contributions:

- A response framework to process (parse and analyze) any natural language specification (*in English*) in order to unveil the intrinsic power structure of a prototype that complies with said specification. The originality of the framework lies in its use of semantic analysis techniques and associated rules to be able to infer the innate power structure that is produced by any prototype following a functional description, typically found in the specification. This power structure (represented by a set of numerical parameters) allows for rapid power-aware exploration of a design, as well as working as a baseline comparison point for decision making regarding the power/energy consumption concerns. The core of the contribution is centered around the associated rules that enable the inference.

- A response framework to process (parse and analyze) any technical language specification (*in SystemC/TLM*) so as to reveal the underlying power architecture that a Virtual Prototype (acting as a functional description) produces by the mere fact of implementing its intended functionality. The originality of the framework lies in a set of algorithms that can extract numerical parameters describing the underlying power architecture. This power architecture comes with both benefits (in reduced power consumption) as well as costs (power and area overhead arising from the need to manage the modules of the IC with extra logic) and these are meant to be taken into consideration as part of the *Design Space Exploration* (DSE) at the system-level in order to decide on the most appropriate power-aware architecture for the design.

Both frameworks constitute a large step towards system-level power-aware specification analysis for ASIC design, as they are able to significantly automate (in as much as possible) tedious tasks that have made system-level power-aware design a laborious process highly dependent on the expertise of seasoned designers. The assistance provided by the frameworks to designers is to be thought of as a systematization of a portion of the designer's system-level expertise within the frameworks.

Part of the research work that leads to the framework has been previously presented in several publications that have been produced throughout the doctoral process. Any content of this document that is not attributed to a third party is either present verbatim in these publications or is a modified form of some content within said publications and is therefore consider own work. The publications are listed as:

- 1. David Lemma, Mehran Goli, Daniel Große, and Rolf Drechsler. "Power intent frominitial ESL prototypes: Extracting power management parameters". *IEEE Nordic Circuits and Systems Conference (NORCAS): NORCHIP and International Symposium of System-on-Chip (SoC)*. 2018.

- 2. David Lemma, Daniel Große, and Rolf Drechsler. "Natural Language Based Power Domain Partitioning". *IEEE International Symposium on Design and Diagnostics of Electronic Circuits and Systems (DDECS)*. 2018.

- 3. David Lemma, Mehran Goli, Daniel Große, and Rolf Drechsler. "Towards Generation of a Programmable Power Management Unit at the Electronic System Level". *IEEE International Symposium on Design and Diagnostics of Electronic Circuits and Systems (DDECS)*. 2020.

#### 1.4 Thesis Structure

After this introductory chapter (Chapter 1), the research work laid out in this document is structured as follows:

- Chapter 2 presents power-aware design as a concept. After a small prelude containing the rationale behind the concept, the implications and challenges in the power-aware design realm are put forward. Further into the chapter, the reader is introduced to the idea of a *Power Management Unit* (the most typical response to the management of the power/energy implications and challenges) with its main defining parameters: the *Power Domains* (PD), and the *Control Signals* (CS) and *Power Modes* (PM). An effective way to determine the PMU parameters from a system-level specification (in natural or technical language) is then shown to be crucial for a successful power-aware design.

- Part I concerns itself with the first contribution (*a framework for the processing of natural language specifications*). Part I consists of a theoretical chapter (Chapter 3) that explains the basics of specification analysis as performed for those documents when they are written in a natural language (English). In addition, there is a relevant works section and a presentation of the framework, based on *Information Extraction* (IE) and semantic analysis techniques (based on a recently developed grammar annotation scheme); and an application chapter (Chapter 4) that shows the applicability of the framework of the previous chapter to the unveiling of the inner power structure caused by the

- specification in terms of some or all PMU parameters (PD, PM and CS) for ASIC type use cases.

- Part II deals with the second contribution listed (how to process a technical language specification in a power-aware fashion). Part II is made of: a theoretical chapter (Chapter 5) that explains the basics of specification analysis as performed for those documents in a technical language at the system-level (Virtual Prototypes in SystemC/TLM). This chapter also contains a section on the relevant works in the field and a presentation of the theoretical framework, based on *Design Understanding* (DU) techniques and tools; and an application chapter (Chapter 6) that shows how the theoretical framework presented in the previous chapter allows for the unveiling of the intrinsic power structure produced by the Virtual Prototypes, a comparison between potential alternatives and an estimation of the effect of the unveiled power structure in the IC's power consumption.

- Chapter 7 brings forth a conclusion to the research work and offers some insights into possible future developments along several research lines branching from the research work.

Power-Aware Design:

Implications, Challenges and

Responses

Power has become the number one problem. All design targets are being constrained by power[21].

— Gary Smith

(Electronic Design Automation analyst)

#### 2.1 Preface

The proliferation of battery powered devices at the end of the 20th century, coupled with an increased awareness of the need to manage power/energy consumption, have been major causes spurring the development of power-aware design for ASICs.

While power consumption and energy consumption are not equivalent, they are both metrics that give information about the fulfilling of the requirements associated with the physical variables involved in the calculation of power/energy. Since energy is a variable derived from power (being the sum of power consumption over a given time period), the latter is the most usual target of many of the techniques developed by the IC design industry. However, power-aware methodologies also consist of techniques that help designers manage energy consumption, via the management of power throughout varying periods of operation, so as to meet any applicable energy budget. (In this document the word power will serve as the generalizing adjective that encompasses both power and energy as described above).

Power, as a magnitude for IC design, can be calculated or estimated by the use of a primary simplified equation. This equation, Eq. 2.1, contains two terms: **static power** and **dynamic power**, which are themselves defined by other simplified equations with their own terms in Eq. 2.2 and Eq. 2.3. **Static power** encompasses

the dissipation of power produced by the IC by virtue of it being connected to an energy source. *Dynamic power* encompasses the dissipation of power by virtue of the IC switching its components according to operational need.

$$P_{total} = P_{static} + P_{dynamic} (2.1)$$

$$P_{static} = V_{cc} * I_{leak} \tag{2.2}$$

$$P_{dynamic} = C * f * V_{cc}^{2}$$

(2.3)

Inside Eq. 2.2 and Eq. 2.3 are several physical variables whose estimated or calculated values are related to the physical synthesis of the circuit (such as voltage  $(V_{cc})$ , capacitance (C), frequency (f) and current  $(I_{leak})$ . In the case of ASICs some of these variables are occasionally dictated and regulated in the specification (typically a technical standard). Regardless of whether or not the variables are directly set in some specification, the physical synthesis stage of the IC design process requires that they are known, as they are crucial in the evaluation of compliance with a power budget.

The terms in the equations are averages (given the simplified nature of the equations), but such equations could be used to obtain a value for power dissipation for every transistor in the IC. Such a value would be extremely accurate, regardless of the fact that is was obtained through the use of averages. This level of accuracy in power dissipation values is typically not feasible in the current state of IC design, since the number of transistors is well beyond the millions. However, provided that the time and computational resources are available, the accuracy of the power dissipation values can be guaranteed to be extremely high at physical synthesis stage.

As power/energy consumption became a crucial design requirement, the way to address the requisite was initially through directly targeting the physically significant variables that affected power dissipation. The techniques developed to manage the physically significant variables constituted the core of what became known as low-power design methodologies [22]. Indeed, by the 1990s and even before that time, power consumption management was characterized by the use of algorithms and heuristic rules that minimized power dissipation as much as it was possible. These algorithms and heuristic rules were focused on lower levels of abstraction (transistor and gate level) where the variables could be directly managed. Furthermore, the

ways in which power dissipation was minimized were mostly orthogonal (that is, independent) of other implications and requirements in the design process.

However, with the growing complexity of ASICs (especially ASSPs), their specifications began to state requirements that greatly influenced each other. This turn of events led to low power design methodologies beginning to fall short of the global integrated approach which came to be required. The EDA industry responded to the challenge by putting forward a renewed set of methodologies, which became known as power-aware design. Closely linked to low power design methodologies, power-aware design and low-power design were not exactly addressing the same concerns. A power-aware system was (and is) not always a low-power system.

As stated by Unsal and Koren [23]:

It is important to note the conceptual difference between power-aware and low-power systems. In low-power design, the main goal is minimization of power. On the other hand, a power-aware system is one in which meeting power and energy goals is a significant design consideration[...]

Low-power design methodologies are usually part of power-aware design methodologies, but do not constitute the totality of them. Furthermore, power-aware design may even preclude the use of some low power design techniques.

Power awareness in methodologies for IC design is meant to meet the power/energy requirements and concerns in a comprehensive fashion. In the words of Pedram and Rabaey [24]:

Just as with performance, power awareness requires careful design at several levels of abstraction. The design of a system starts from the specification of the system functionality and performance requirements and proceeds through a number of design levels spanning across architectural design, register transfer level design, and gate level design, finally resulting in a layout realization.

As per the shift to power-aware design methodologies, many of the associated techniques ceased to be only concerned with the direct management of the physically relevant variables at lower levels of abstraction. In raising to gate level and even to the *Register Transfer Level* (RTL), both the detailed information of physical synthesis stage and the ability to directly control the physically relevant variables are reduced.

In higher levels in the abstraction ladder (for instance, a system level such as the ESL-Electronic System Level) the accuracy in the calculation/estimation of power

dissipation is lowered as per the increased abstraction. The reduced accuracy is the result of lacking the detailed information that is available in physical synthesis stages. At the same time, the effect on the management of power consumption of whatever techniques used by the power-aware methodology at hand becomes increasingly noticeable. In many cases, techniques that are part of the power-aware design methodology at system-level are less focused on optimization of a given architecture than they are about being useful to architectural decision making. The impact of architectural decision making can be shown via a design level ladder featuring the different the different design stages.

#### 2.2 Implications

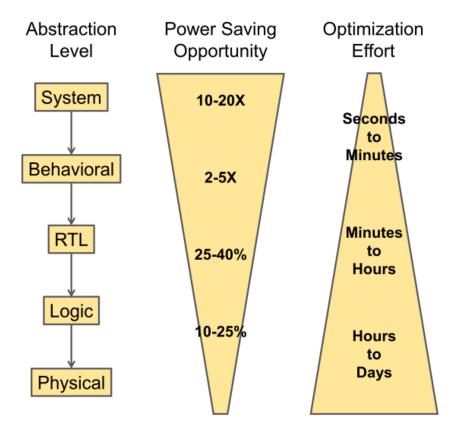

As can be seen in Fig. 2.1, the nature of the design level ladder is well represented by pyramids depicting the power saving opportunity and the optimization effort involved for each level, from the system level to the physical level. Following a top-down perspective, it is becomes clear that on a system level, the impact of the techniques used by a power-aware methodology is at its highest, with the effect (power saving opportunity) not only decreasing significantly in lower levels of abstraction, but also requiring much more optimization effort. While the accuracy in the estimation of the effect at higher levels of abstraction is much lower than closer to implementation levels (eg. gate level), the dissimilar orders of magnitude of the estimated effects make it a compelling reason for the EDA industry to focus heavily on sound architectural decision making techniques.

Architectural decisions typically encompass a process of specification analysis that is done within a set of processes that the IC design industry labels *Design Space Exploration* (DSE) [26] [27]. DSE is a set of processes that attempt to compare and contrast different architectural alternatives that follow the specification for a given design. Typically, low abstraction level DSE is the realm of multi objective optimization algorithms with special focus on finding the optimal solution from within the different architectural alternatives [28]. In order to perform DSE at a high abstraction level it is paramount to be aware of the intended functionality of a system. Such an awareness typically entails knowing how the functional tasks of the design are implemented [29]. Both the originally devised architectural alternatives and the potential optimized solutions are presented in terms of the components at different level of abstraction, as components encapsulate and abstract away many (if not all) of the design factors present at the set of simplified power equations previously presented.

Fig. 2.1: Design Level Ladder and its Impact on Power from [25]

Based on the concept of component, the implications of a proper power-aware DSE process become easier to describe. Consequently, to conduct power-aware DSE on a given system provided by an IC it becomes necessary to analyze the impact of the components on the way power is consumed and on how it should be managed. The power structure, which is the byproduct of the intended functionality of a system, is defined by the boundaries and interactivity of the components and needs to be properly known. Whatever chosen arrangement (architecture) of the components, as well as the power structure they entail, needs to also be evaluated in light of both their fulfillment of the functional tasks required by the design and their impact on the way power is managed by the design (for its benefits and associated costs).

For the results of power-aware DSE to be of any practical use, the functional tasks that the system should be themselves be examined through a profiling process. The process of profiling the functional tasks can be summarized as the characterization of the active/inactive periods of the systems as dictated by the fulfillment of the tasks. The profiling process done on the functional tasks can be performed independently of any decision concerning the components, but the former affects the latter and

Fig. 2.2: Design Levels and Design Tasks Associated with Them based on [30]

should be thought of as the main starting point of power-aware DSE at higher levels of abstraction (such as the system levels).

#### 2.3 Challenges

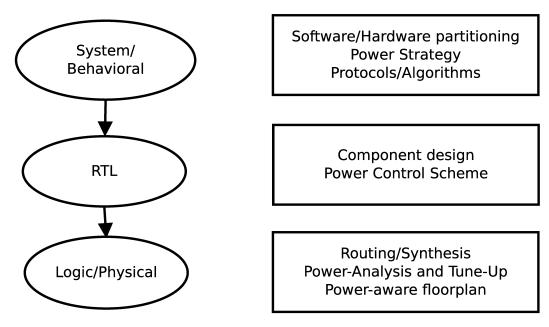

The series of steps that summarize power-aware DSE are summarized in Fig. 2.2. By looking at it, it becomes noticeable that the step at the top of the figure, under *System Design*, deals with tasks of planning nature that are run at system level, establishing the architecture of the IC. Among the tasks is deciding *Power Strategy*, which is obviously the most important factor when designing an architecture (a power structure) to back said strategy. Whatever functionality decision taken at the beginning stages of the IC design process is linked to a similar decision related to power at a similar stage. For instance, once the design reaches the RTL stage, the *Power Control Scheme* needs to be decided on and subsequently verified. Furthermore, in the implementation stage, which encompasses the logic and physical level in Fig. 2.1, *Power Analysis and Tune-up* are important power-aware tasks, alongside deciding on the *Power-aware floorplan*.

Power-aware design methodologies must enable sound architectural decisions that meet both functional and power related requirements. In addition to the need for judicious architectural decisions that fulfill both functional and power related requirements, whatever resulting byproduct of these decisions, should be analyzed in

| Technique             | Description                                                                                           |

|-----------------------|-------------------------------------------------------------------------------------------------------|

| Clock gating          | Disables clock tree part not in use. Synchronous block stop its operation.                            |

| Operand isolation     | Prevents switching of inactive datapath element.                                                      |

| Logic restructuring   | Moves high switching logic to the front and low switching logic to the back.                          |

| Transistor resizing   | Upsizing reduces dynamic power, downsizing reduces leakage power.                                     |

| Pin swapping          | Swaps the gate-pins in order the switching to occure at pins with lower capacitive loads.             |

| Multiple supply       | Different blocks are operated at different (fixed) supply voltages. Signals that cross voltage domain |

| voltages              | boundaries have to be level-shifted.                                                                  |

| Dynamic voltage       | Different blocks are operated at variable supply voltages. Uses look-up tables to adjust voltage on-  |

| scaling               | the-fly to satisfy varying performance requirements.                                                  |

| Adaptive voltage      | Different blocks are operated at variable supply voltages. The block voltage is automatically         |

| scaling               | adjusted on-the-fly based on performance requirements.                                                |

| Frequency scaling     | Frequency of the block is dynamicaly adjusted. Works alongside with voltage scaling.                  |

| Power gating          | Turns off supply voltage to blocks not in use. Significantly reduces the leakage. Block outputs float |

|                       | and need to be isolated when connected to active block.                                               |

| State retention power | Stores the system state prior to power-down. Avoids complete reset at power-up, which reduces         |

| gating                | delay and power consumtion.                                                                           |

| Memory splitting      | The memory is splitted into several portions. Not-used portions can be powered down.                  |

Fig. 2.3: Frequent Power management Techniques from [31]

comparison to potential alternatives. Typically, high level decisions of architectural nature reduce the number of potential alternatives in the design, which implies the use of a particular set of power management techniques. A set of power management techniques applied in a defined way constitute a power strategy, whose effectiveness and associated costs should be properly analyzed.

A *Power Management Strategy* (PMS) (also known as a Power Strategy) is pursued by the rational application of the adequate set of power management techniques. Some of these techniques (presented by D. Macko [31]) are listed in Fig. 2.3. Many such techniques are susceptible to classification under the abstraction level which they most prominently target. Typically, techniques related to direct effects on physical variables that are responsible for power dissipation (eg. voltage, capacitance and current) are targeted at transistor and gate levels. Techniques that indirectly affect the physical variables are typically used at higher levels of abstraction (eg. the RTL and system levels). In any case, techniques are to be applied throughout the entire design process [32] [33].

Any set of power management techniques may also be sorted into categories according to the term (dynamic or static power) of Eq.2.1, that they most directly impact. Such a simplified classification is neither unreasonable nor arbitrary, since the concepts of dynamic and static power remain extremely relevant in the general literature in the field. A key example of the relevancy of classifying power management techniques according to their influence in terms of the more generalized dynamic or static power can be seen in Table 2.1. In this table, besides their influence on dynamic or static power, the impact of some of these techniques in area and power overhead, as well as in the overall design are also shown to be different. It is

then evident that power management techniques need to be used concurrently for most IC.

Tab. 2.1: Some Power Management Techniques and Their Impact

| Power<br>Management<br>technique       | Static<br>Power<br>influence | Dynamic<br>Power<br>influence | Area<br>overhead | Power<br>overhead | Impact<br>on<br>overall<br>design |

|----------------------------------------|------------------------------|-------------------------------|------------------|-------------------|-----------------------------------|

| Clock Gating                           | 0                            | Very high                     | Low              | Low               | Medium                            |

| Power Gating                           | Very high                    | 0                             | Medium           | Medium            | High                              |

| Dynamic (Voltage)<br>Frequency Scaling | Medium                       | High                          | High             | Medium            | Very high                         |

While (re)producing an exhaustive list of power management techniques is not within the purview of this chapter, the techniques listed in Table 2.1 are further explained in the next paragraphs. These power management techniques are well known for their impact extending all throughout the abstraction ladder. It is because of the influence of these techniques on the effectiveness of the PMS that an intelligent application of them is of extreme importance. The techniques are: *Clock Gating* (CG) and *Power Gating* (PG) and *Dynamic (Voltage) Frequency Scaling* (DVFS):

Clock Gating (CG): is a technique based on switching off the clock signal for any given component whenever there is no need for said component to switch its internal state. The granularity with which the technique is applied can vary from gate level to RTL and beyond. As the signal under management is that of the clock, the dynamic power term of the total power equation is the one impacted, whereas the static term is not. Despite the absence of influence on static power consumption, the technique is widely used as typical ASICs have extremely large and complex clock trees for which pruning yields valuable results. CG is typically implemented at RTL or gate level, but the general principle operates on the behavioral level and the system level.

**Power Gating (PG)**: is a technique based on switching off the voltage supply from any given component whenever there is no need for said component to be in operation. Typically, this technique is based on examining the active/inactive cycles of components so as to power off those in their inactive cycles. The fact that voltage supply is cut off from any given component (that is, it is made 0), essentially means that the impact on the static term constitutes the salient point of the technique. PG, like Clock Gating, is implemented at RTL or gate level, but its roots are at behavioral and system level. Unlike Clock Gating, PG greatly affects the static power term of the total power equation.

Dynamic (Voltage) Frequency Scaling (DFVS): is a technique by which any given component of the IC (typically a design element at the RTL, such as a buffer, a register, an adder, etc.) is run at a certain voltage and frequency value pair that maximizes its output or general performance while remaining under the power or energy budget. In general, low voltage-frequency value pairs reduce power consumption at the expense of performance degradation. However, given that performance requirements are neither static throughout the operation of the IC, nor homogeneous for every component, DVFS is a feasible attempt to reach a desirable tradeoff, typically being a technique in widespread use at the RTL, affecting both the dynamic and static power terms of the total power equation.

While the aforementioned techniques have a direct influence on physical variables (voltage, frequency), they also have an indirect effect on them via the architectural impact on ICs produced by the power management logic required for their application. In order to apply DVFS, CG or PG in an IC, the latter has to contain proper power management logic, which leads to associated overhead costs (such as the extra power dissipated by the required by the new logic or the increased area required by the physical synthesis of said new logic). The associated overhead costs can be thought of as one of the most evident and inevitable tradeoffs in the selection of a PMS.

#### 2.4 Responses

It is a fairly common occurrence for the PMS to be carried out by a *Power Management Unit* (PMU). An illustrative PMU is made of a component with control over the power management logic. In ASICs, the PMU is frequently a very simple structure which drives signals controlling the execution of the chosen power management techniques as they are applied to control all other components. Frequently containing a type of Finite State Machine, a PMU has the PMS encoded in its own structure. By being the vessel than ensures the implementation of the power management techniques, the joint associated costs of these techniques can be summarized as the overhead costs of the PMU itself.

#### 2.4.1 Power Management Unit (PMU)

The PMU itself (being a virtual aggregation of the power management logic of an IC) leads to an increased power consumption, even when one of the typical main goals

behind the existence of such a unit is to reduce the overall power consumption of the IC. The overhead costs of the PMU are therefore of great importance following the corollary behind the statement "spend power to reduce power". Furthermore, the architectural impact of the PMS, which is represented by the structure of the PMU, acquires relevancy as it can lead to increased difficulty in validation and verification tasks both for the PMU and for the overall IC design.

Given the need for a Power Management Strategy for any properly designed ASIC, the associated costs of realizing that strategy (the implications of power-aware design) need to be handled carefully within the PMU. The PMU has to be designed in a power-aware manner, following successful DSE tasks that: effectively deal with the collateral effects of the PMU on any given ASIC (such as extra power consumption and endogenous verification effort already mentioned), minimize the expected extra management logic (reducing the area required for physical synthesis) and ensure that any concomitant power related decision is made in harmony with any non power related concern.

Decisions on the validity and proper implementation of the PMS in the PMU are dictated by how satisfactorily said strategy addresses power related requirements (for instance, the meeting of a power budget). In order for the decisions to lead to proper responses that fulfill a power related requirement, the tasks that provide the basis for the making of those decisions must be not only technically fitting, but also comprehensive. The rationale behind technically fitting, comprehensive power-aware DSE tasks leading to sensible decisions is in the global, architectural impact of the latter.

As a PMU represents the embodiment of the PMS, the architectural impact can be represented via the influence of the latter on two important notions: the functional block and the area overhead. These two notions showcase the variables that the PMS both affects and becomes affected by and underscore the comprehensive nature of the power-aware DSE tasks required to successfully implement the PMU. As such, the notions are elaborated as follows:

• A *functional block* is the label for the constitutive elements of components, a label that can be applied in different stages in a design flow. Being so widely applicable as a concept means that a functional block can be: a collection of gates and other similar elements working together in combinational or sequential logic (at the RTL), a set of algorithm-implementing objects representing an assortment of units at RTL (when considering the concept at the ESL, where algorithms are implemented) and even a series of self contained

system level components seemingly working as blackboxes (at the specification based system level).

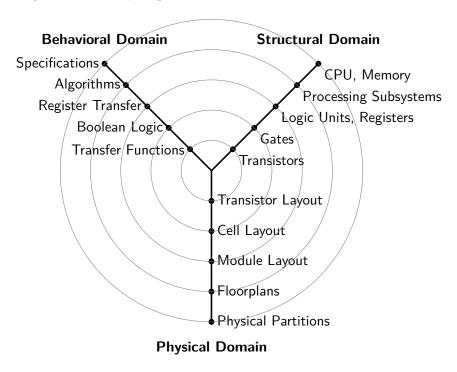

In a Gajski-Kuhn Y diagram [34] such as the one depicted in Fig. 2.4, the concept of functional block is reflected by the bisecting domain labeled "Structural". Along the arrow (from the center to the most external node) that states the elements of the structural domain, every element is matched to an abstraction level (Transistor Level, Gate Level, RTL, Algorithmic Level, System Level). The same type of matching is available for every element in both the arrows for Behavioral Domain and Physical Domain The Y diagram is a graphical way to understand the importance of the concept of functional block not only within the Structural Domain, but also within the Behavioral and Physical Domain.

The elements of the Structural Domain correlate with elements of the Behavioral and Physical Domain for each level. Such relations only underscore the relevance of the functional block for a comprehensive analysis of the design process. Typically, the highest level of abstraction in the design ladder (the System Level) ties in the functional block concept to the specifications of the design, as well as relating it to the global physical partitioning of the chip that the specification may require.

Fig. 2.4: Gajski-Kuhn Y Diagram

For ASICs or ASSPs, the specifications typically describe the functionality required of the circuit through listing the algorithms that define it, through naming the functional blocks that perform the functional tasks required of the design and also through the placement of relevant system wide constraints (eg. a power/energy budget, a security or safety check). In this document, the system wide constraints that become the focal point are those related to power management. However, a power budget is not the only system wide constraint that relates to power management.

There is a systemic influence of the power management as a concern in any design process. Such systemic influence means that the implementation of the power management strategy for the IC should be taken so as to comply with a power budget, security/safety checks, while also properly dealing with the inevitable extra circuit logic required. The additional logic is typically an undesired byproduct of the implementation of the PMS, one that should be minimized as much as possible.

When considering the impact of the extra circuit logic, a power-aware design flow usually leads to a trade-off. The more sophisticated (and potentially more power-aware) the PMS, the bigger the extra circuit logic required. This rule of thumb is not meant to be taken as a strict correlation, but nonetheless serves to illustrate the need for a balance between two potential factors: power efficiency and extra management logic. So as for a better understanding of the impact of the extra power management logic, such an impact is described by a second notion: area overhead.

• The *area overhead* of the implementation of a PMS is a concept that is representative of the amount of transistors, gates and other functional blocks that said implementation requires. This amount is, naturally, in addition to whatever was required for the implementation of the functionality of any intended design, which is consistent with the use of the word "overhead". Given the fact that area is a constraint in the synthesis of current (and foreseeable) ASICs, any overhead in this metric is to be carefully dealt with.

While the concept of area overhead is closely linked to lower levels in the abstraction ladder, the effects can be observed beyond the Gate Level or the RTL. Not unlike the notion of functional block, the area overhead resulting from extra power management logic can be considered throughout the levels of the Gajski-Kuhn Y diagram. Once again, the prototypical functional block for each level can be considered as the constituent element of the implementation of the power management logic.

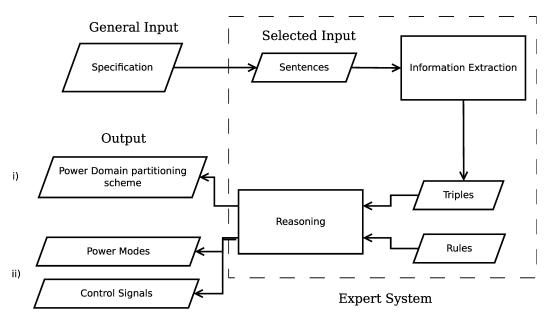

Among the most important decisions that underpin the architectural impact of the power-aware DSE tasks that influence the notions above are: a) **Power Domain** (PD) partitioning and b) the setting of **Control Signals** (CS) and **Power Modes** (PM). The preceding decisions are naturally based on the power structure that is revealed by inspecting the specification, which yields PD, CS and PM. The frameworks that allow for this inspection to reveal the underlying power structure are the contributions of this thesis, laid out in the theoretical chapters of Part I and Part II.

So as to clarify what is meant by PD, CS and PM, the following are non exhaustive, but clear definitions:

#### 2.4.1.1 Power Domain

A **Power Domain** is a collection of functional blocks that share the same voltage source and can be considered a single group whose power can be managed independently from other parts of the design. For example, functional blocks that operate whenever a device is powered are typically part of an Always-ON Power Domain, whereas other functional blocks that are activity dependent are typical part of other Power Domains.

#### 2.4.1.2 Control Signal

A **Control Signal** is the way in which a Power Domain is driven ON/OFF (or into a different power state) as per dictated by the PMS. For many designs it is reasonable to assume that each Power Domain will have at least one Control Signal to drive it, but this Control Signal could potentially have different values leading to independent and concurrent control of several of those Power Domains.

#### 2.4.1.3 Power Mode

A **Power Mode** is a given set of the power states (ON, OFF, other) of the Power Domains during the operation of a circuit. It is therefore, a way to identify the system wide operational status of a design. Examples of Power Modes are: ACTIVE, ON, IDLE, SLEEP, OFF, etc.

#### 2.4.1.4 Power Domains, Control Signals and Power Modes and the PMU

The revelation of the implicit power structure is the basis for the handling of the PD, CS and PM that are associated with said power structure. Decisions relating to how the PMU is to properly address the management of power rely on the number of PD, CS and PM. Consequently, in the following paragraphs the reader is very succinctly introduced to the basics of both PD partitioning and the setting of CS and PM.

**2.4.1.4.1 Power Domain Partitioning** Power Domain (PD) partitioning is a process that deals with the organizational structure supporting the PMS. In essence, Power Domain Partitioning is the process by which such structure is decided upon. As a power-aware DSE task, it is typically the first critical decision making process. As such, Power Domain Partitioning is a key step in setting the basic architecture of the PMU.

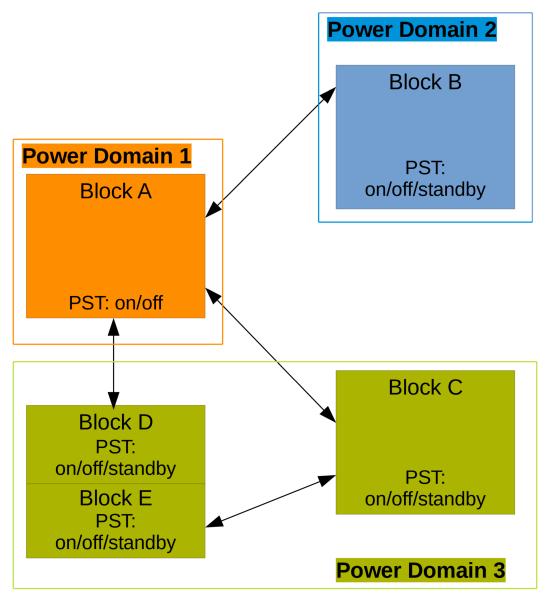

The essence of Power Domain partitioning is, as would be expected, the concept of a Power Domain (PD). How to arrange the functional blocks in different PDs is the core of the Power Domain partitioning decision. As illustrated by Fig. 2.5, the process chiefly sorts the different functional blocks of a design into groups (the Power Domains). The power properties of these groups (such as, for instance power states-on,off,standby) can then be managed independently from each other. As evidenced in the figure, three functional blocks (Block C, Block D and Block E) can be part of the same power domain (Power Domain 3) if they share the same Power State Table (PST). However, this may not be desired if the designer wants to manage each of the blocks individually. A decision on the convenience of such an arrangement (the Power Domain Partitioning scheme) is the designers' responsibility.

Typically a fine grained Power Domain partitioning scheme leads to many PD (the maximum would be given by the number of functional blocks, with one PD per functional block) and an unavoidable area overhead. A more coarse grained approach to Power Domain Partitioning usually leads to a scheme with reduced area overhead and fewer PD, but at the cost of missing power consumption reduction opportunities. The opportunities for power consumption reduction are missed on account of the impossibility to control the power states of each functional block individually, since said blocks will be part of the same PD.

To group certain functional blocks together has a deep impact not only on power consumption, but also on further verification efforts, both for the overall design, and for the PMU executing the associated power management strategy, as shown by Agarwal et al. [36] and Wang et al. [37]. The deep impact is also felt in the overall

Fig. 2.5: Example of a Power Domain Partitioning Scheme from [35]

verification efforts for the design, which once again highlights the tremendous importance of deciding on a proper Power Domain partitioning scheme for power-aware design at system level.

**2.4.1.4.2 Setting of Control Signals and Power Modes** The Setting of Control Signals (CS) and Power Modes (PM) is a process that details the architecture of the PMU. Usually done after the PD partitioning process (it can also be done concurrently with the PD partitioning process), the setting of Control Signals and Power Modes is the cornerstone of the PMU, a process whose objective is to establish the way of

operation of said PMU. In essence, CS and PM are numbers defining the behavior of the PMU, which, in itself, represents the way the PMS is put forward.

For the PMS to be properly deployed, the PMU additionally needs to have the system Power Modes (such as, for instance, IDLE, ACTIVE, INACTIVE modes) and Control Signals (which drive the power domains) set. Both PM and CS are widely influential PMU design parameters. Regardless of how the decision about the determination of the aforementioned parameters is reached, PM and CS will reflect the complexity of the PMS, which it itself signals the complexity of the PMU.

Just as is the case of a power domain partitioning scheme, the number of Power Modes and Control Signals are important because they are usual indicators of the power intent (that is to say, the power management strategy). The impact of both PM and CS on the overall costs (mainly amounting to verification time, power consumption and area overhead) of a PMU is as important as that of the Power Domain Partitioning process. This impact means that the PM and CS need to be determined as early as possible in the design flow [38].

A suitable set of assumptions are necessary to keep the approach to determining (and thus setting) both PM and CS as simple as possible. For instance, a simplified version of the process can have as premises: a single CS can power ON/OFF a Power Domain (no complex individual Power States, such as IDLE or SLEEP); and a Power Mode represents a system wide state (one where the state of each Power Domain is ascertained), which can be ACTIVE, IDLE, SLEEP or similar.

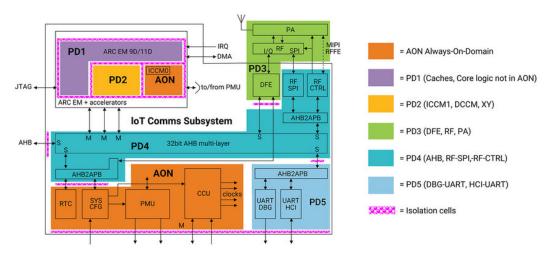

As a graphical example, please consider Fig. 2.6 and Fig. 2.7, which show a Power Domain Partitioning scheme and a table summarizing the Power Modes and Power States for a device. These figures are taken from the description of an IoT device which has a RF transceiver and an ARC EM processor, suitable for a well known 3GPP standard [39].

The figures show 6 PD (AON, PD1, PD2, PD3, PD4, PD5, PD6) in the bottom rows, 3 PM (ACTIVE, SLEEP and STANDBY) on the columns, and the Power State, controlled by a CS, for each of the PD (ON, OFF, "rentention"). This a typical Power Management scheme, consisting of enough PD, CS and PM, to presumably guarantee a low power consumption for a battery powered device without needlessly increasing the complexity of the PMU (which is on the AON-Always ON domain).

Research has been conducted for the complexity costs, concluding in a rule that basically leads to two statements:

Fig. 2.6: An IoT Device's Power Domain Partitioning Scheme from [39]

| POWER MODE     | ACTIVE         | SLEEP                        | STANDBY  |

|----------------|----------------|------------------------------|----------|

| EM Processor   | RUN (SLEEP0-3) | SLEEP4                       | SLEEP5   |

| RF Transceiver | TX / RX / IDLE | IDLE                         | POWEROFF |

| Power Domain   |                |                              |          |

| AON            | ON             | ON                           | ON       |

| PD1            | ON             | OFF                          | OFF      |

| PD2            | ON             | rentention<br>(all memories) | OFF      |

| PD3            | ON             | ON                           | OFF      |

| PD4            | ON             | OFF                          | OFF      |

| PD5            | ON             | OFF                          | OFF      |

Fig. 2.7: An IoT Device's Power Modes and Power States from [39]

- The number of PM and CS can be used to predict the power consumption of the PMU (with the CS having a greater impact than the PM, due to more CS requiring more area in silicon which will dissipate more energy)

- The number of PM and CS correlate greatly with the time needed to be spent on the verification of the PMU (with the PM having a great impact than the CS, because of the implications of PM in the number of transitions to validate)

Because of those two statements, the designers need to be careful about choosing the most appropriate Power Partitioning scheme, as well as with choosing the amount

of Control Signals and Power Modes that the PMU will implement. The fact that the PMU itself needs to be considered another functional block in an Always ON domain also highlights that the decisions need to be taken before the RTL, that is, before the microarchitecture of the system has been established.

The most natural way to decide the setting of PD, CS and PM is, therefore, to focus on a higher level of abstraction: the system level. In said level, the most typical design documents available are: a *natural language specification* (typically in English) or a *technical language specification* (typically in SystemC/TLM).

As stated in the Introduction chapter to this document, this thesis presents two frameworks that allow for the power structure that is intrinsic to a design to become available to those responsible for implementing the PMS within the PMU. The PD partitioning scheme and the setting of the CS and PM depend on the availability of the implicit power structure for the cases of a design following both a natural language specification (which is dealt with in Part I) or a technical language specification (dealt with in Part II).

Part I: Natural Language Specifications Natural Language:

Preliminaries, Relevant Work

and Response Framework

## 3.1 Preliminaries

It is fairly common for designers to have specifications as their initial design documents when they are following a top-down design pattern. It is also common that, even before a specification is written, there are algorithms, flow or block diagrams that make intuitive sense to designers. Unfortunately, the very essential informal design documents that constitute the basic design idea are rather ambiguous and usually come as a response to a set of requirements that have to be met. When the way in which these early stage documents concerns themselves mainly proper elicitation of the requirements, the documents are best approached by requirement engineering [40].

If a specification is available, it is frequently one written in a natural language, such as English, either in an informal descriptive tone or a more formal tone, such as the case of a (technical) standard, very common for ASICs. In the latter case, it is also quite likely that there exists a reference implementation described within the standard or in a closely associated, yet separate document. Standard specifications (usually shortened to standards) are often described as documents expressing a series of characteristics provided by an implementation. For digital circuits and related Systems-on-Chips (SoCs) these characteristics pertain mostly (but not exclusively) to functionality and are typically covered in one or several chapters of the appropriate standards. The designers are expected to comply with and follow the standards, so as to produce validated implementations.

Traditionally, standards are long dense documents with tables, diagrams and text detailing the underlying several aspects, attributes and features of blocks/components/elements of a system. Because of the sheer volume of information contained in a standard, the examination of one is almost invariably done by experienced design-

ers. This process includes the laborious elicitation of relevant data and knowledge from the contents of the standard, as well as any needed interpretation.

Given the opportunity, streamlining the laborious process of data and knowledge elicitation appears to be a natural step forward. To decrease the effort required for the manual elicitation of data and knowledge, Information Extraction (IE) is typically used [41]. As a well known way to push for the automation of the analysis of standards IE consists of a series of techniques to bring out relevant data. As a general purpose toolset, IE features two common approaches are: i) domain specific Information Extraction or ii) Open Information Extraction (OIE). As the name of the former suggests, the approach based on it, focuses on retrieving relevant information (facts) only on a very specific field (domain). This is usually aided by a robust concept corpus (typically, an ontology) and by the use of other additional knowledge sources [42] [43]. Contrary to this, OIE aims for general all purpose information extraction or retrieval from texts of varied topics, styles and sources. For OIE, there is a tradeoff between precision (retrieving all the useful facts) and recall (retrieving only the useful facts). For a succinct explanation of the concepts, please take into account that: i) precision may be defined as the number of true positives (the useful facts), divided by the number of selected elements (the total number of facts retrieved), ii) recall may be defined as the true positives (the useful facts) divided by the number of relevant elements (the total number of relevant facts). For both precision and recall the number defining them (the score) is between 0 and 1. Both these values are usually provided as a means of assessing the quality of the results provided by the OIE tool, but do not ensure that the results are of any use for further understanding or reasoning.

A useful fact is one germane to the understanding or description of a text based on its domain. For instance, a fact such as "The circuit is internally connected through wires" is typically too evident to constitute a useful piece of information, whereas "The circuit has a output serial port" is a fact that provides significant information that can be used to understand the text. Analogously, relevant facts are considered facts that are not tautologies (redundancies) or grammar based constructs devoid of significance in the context of the domain. For instance, a fact such as "The digital circuit consists of digital components" is not a relevant fact, since it is redundant, whereas "The digital circuit consists of an encoder and a UART" is a relevant fact since the added information leads to further understanding.

If OIE is used for domain specific information extraction, the desired recall is usually of higher importance than the desired precision. This is so because a high number of relevant but not useful facts can be discarded if needed further down the processing

32

tasks, whereas non relevant facts can be harder to discard if they are firstly grouped together with relevant ones. However, a high number of both precision and recall (such as for instance, a high F1 score) are generally desirable, even if rather difficult to attain.

Approaches using OIE tools are more frequently researched than those using the domain specific counterparts. Two key reasons behind this fact are: a) the desire to make the approach as universal as possible and, b) the lack of an ontology or a similar domain specific knowledge source. Notwithstanding the preference for OIE tools, whatever approach to the analysis of standards can also work with domain dependent IE tools. If a domain dependent IE tool is available and is wisely used, it will most likely lead to more refined scrutiny than the OIE alternative.

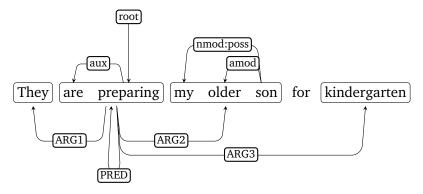

OIE is routinely characterized as a task, in which the techniques used are grouped into diverse subtasks (Entity Extraction, Relationship Extraction, Word Sense Disambiguation, Coreference Resolution, Terminology Extraction and many more than tightly relate to *Natural Language Processing* (NLP)). Without entering into too much detail, two of the tasks listed above are extremely central to analyzing a text with semantic understanding as a goal: *Entity Extraction* and *Relationship Extraction*. For a short explanation it can be said that the former retrieves relevant (for whatever domain) entities (traditionally considered concepts-self standing notions), whereas the latter retrieves the association that binds the entities.

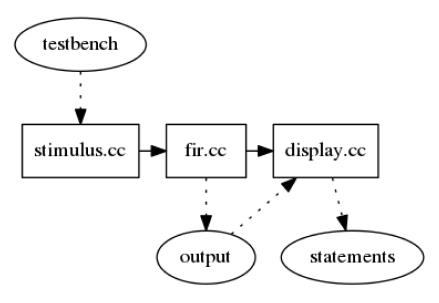

For a clearer explanation of both subtasks, please consider the following sentences from the README file (an informal specification in natural language) of an example FIR filter, a very basic design that comes with the official SystemC distribution suite from Accellera [44].

"The filter is a 16 tap FIR filter(fir.cc). The test bench feeds simply ascending values into the FIR(stimulus.cc) and the output is sampled (display.cc) and displayed with print statements."

Entity Extraction will yield a series of entities that can be pruned later, either by humans or by some automated procedure. A list of entities may be similar to that in Table 3.1. Here, anyone familiar with the field of digital circuit design will notice that *fir* and *fir.cc* refer to the some entity, not unlike the case for *output* and *display.cc* and *value* and *stimulus.cc* (which refer to the input of the circuit). Because of these equivalences, refined Entity Extraction leads to semantic entities, that is to say, entities which are not mere language artifacts, but meaningful concepts within the domain.

Tab. 3.1: Entity Extraction