# Systematic Design of Low-power Processing Elements Using Stochastic and Approximate Computing Techniques

Dissertation zur Erlangung des akademischen Grades Doktor-Ingenieur (Dr.-Ing.) im Fach Elektrotechnik und Informationstechnik

# Ardalan Najafi

Gutachter: Prof. Dr. Alberto García-Ortiz

Gutachter: Prof. Dr. Guillermo Payá Vayá

Eingereicht am: 21.12.2020 Tag des Promotionskolloquiums: 26.01.2021

© 2021 Ardalan Najafi ALL RIGHTS RESERVED

#### **Abstract**

The approximate and stochastic computing have been developed, on the one hand, to address the diminishing gains of technology scaling, and on the other hand, to exploit the intrinsic error resilience of many applications. They, indeed, take advantage of the disparity between the level of accuracy required by the application and that provided by the computing system, for achieving energy efficiency. As of the most important constitutes of an integrated circuit, arithmetic units often lie within the critical path of a processing system. They play a vital role in determining the performance and power consumption of the computing system.

In the past decade, the design of the approximate arithmetic units has been in the center of attentions of the VLSI design research community; resulting in a numerous proposed approximate designs in the literature. In spite of a decade work on the approximate computing, there are still unresolved challenges faced by digital designers.

The concept of acceptable quality of the results forms the foundation of the approximate and stochastic computing. In view of this fact, it is crucially decisive to have a clear, quantifiable definition of what signifies an acceptable quality. Indeed, the current metrics most often do not capture the requirements of a target application, and hence, mislead to sub-optimal design options for the application. Moreover, non-systematic designs, lack of fair comparisons and reproducible research have resulted in somewhat limited progresses in the field of approximate and stochastic computing. Besides, the accuracy requirements of an application is not a static property and may change across the different phases of the application. Therefore, it is important to systematically develop approximate and stochastic computing platforms which offer a variety of output qualities.

In this dissertation, the aim is to take fundamental steps towards resolving the aforementioned challenges. Correspondingly, the following contributions are made in this dissertation. First, to palliate the lack of expressiveness of current metrics, a new parameterizable metric which correlates more precisely to the accuracy of the applications is proposed in this dissertation. Afterwards, the importance of fair comparisons for approximate computing units is underlined in this work. Subsequently, through generalizing and systematically optimizing an architectural template for approximate adders, an architecture is proposed which outperforms its existing counterparts. A conceptual framework for the systematic design of approximate adders including hybrid and non-equally segmented approaches is developed next. The framework discriminates the scenarios where approximate processing does not provide significant benefits from those where it does; in this latter case, it aids in obtaining optimal configurations for the adders. Furthermore, in order to address the dynamic

configuration of the error characteristics, a stochastically-tunable adder is proposed which reduces the energy-delay product considerably in comparison with its conventional counterpart. In addition, we develop data-dependent corrections for truncated multipliers, where the proposed architectures surpass the existing approximate multipliers in the literature.

The applicability of the proposed methods, and in general approximate computing units is eventually studied in modern applications. The correlation between the errors of a single unit and the whole system's accuracy is also investigated in the applications.

# Kurzfassung

Die approximative und stochastische Berechnung wurde entwickelt, um einerseits die abnehmende Gewinne der Technologieskalierung zu adressieren und um andererseits die intrinsische Fehlerresistenz vieler Anwendungen auszunutzen. Sie nutzen den Vorteil der Diskrepanz zwischen der von der Anwendung geforderten und der vom Rechensystem bereitgestellten Genauigkeit, um eine Energie-Effizienz zu erzielen. Als einer der wichtigsten Bestandteile einer integrierten Schaltung liegen Recheneinheiten oft im kritischen Pfad eines Verarbeitungssystems. Sie spielen eine wesentliche Rolle bei der Bestimmung der Leistung und des Stromverbrauchs des Rechensystems.

Im vergangenen Jahrzehnt stand der Entwurf der approximativen Recheneinheiten im Zentrum der Aufmerksamkeit der VLSI-Design-Forschungsgemeinschaft, was zu zahlreichen Vorschlägen von approximativen Designs in der Literatur führte. Trotz der Arbeit eines Jahrzehnts mit approximativen Recheneinheiten gibt es immer noch ungelöste Herausforderungen für digitale Designer.

Das Konzept der akzeptablen Qualität von Ergebnissen bildet die Grundlage für die approximative und stochastische Berechnung. In Anbetracht dieser Tatsache ist es von entscheidender Bedeutung eine klare, quantifizierbare Definition dessen zu haben, was eine akzeptable Qualität bedeutet. In der Tat erfassen die aktuellen Messwerte meist nicht die Anforderungen einer Zielanwendung und verleiten daher zu suboptimalen Designoptionen der Anwendung. Außerdem haben unsystematische Designs, fehlende faire Vergleiche und reproduzierbare Forschung eher begrenzte Fortschritte auf dem Gebiet der approximativen und stochastischen Berechnung nach sich gezogen. Darüber hinaus sind die Genauigkeitsanforderungen einer Anwendung keine statische Eigenschaft und können sich über die verschiedenen Phasen der Anwendung ändern. Daher ist es wichtig, systematisch approximative und stochastische Berechnungsplattformen zu entwickeln, die eine Vielzahl von Output-Qualitäten bieten.

In dieser Dissertation sollen grundlegende Schritte zur Lösung der oben genannten Herausforderungen unternommen werden. Dementsprechend werden die Beiträge dieser Dissertation folgende sein: Erstens, um die mangelnde Aussagekraft aktueller Messwerte zu lindern, wird ein neuer parametrisierbarer Messwert in dieser Dissertation vorgeschlagen, der präziser mit der Anwendungsgenauigkeit korreliert. Anschließend wird die Bedeutung fairer Vergleiche für approximatives Computing in dieser Arbeit hervorgehoben. Darauffolgend wird durch Verallgemeinerung und systematische Optimierung einer Architekturvorlage für approximative Addierer eine Architektur vorgeschlagen, die ihr existierendes Gegenstück übertrifft. Als Nächstes wird ein konzeptioneller Rahmen für den systematischen Entwurf von approximativen Addierern einschließlich hybrider und nicht-gleich-segmentierten Ansätzen entwickelt. Die Rahmenkonstruktion unterscheidet die Szenarien, in denen die approximative

Verarbeitung keine signifikanten Vorteile bietet, von denen, in denen sie signifikante Vorteile bietet; im letzteren Fall hilft sie bei der Erlangung optimaler Konfigurationen für die Addierer.

Weiterhin wird ein stochastisch abstimmbarer Addierer vorgeschlagen, um die dynamische Konfiguration der Fehlereigenschaften zu berücksichtigen, der das Energieverzögerungsprodukt im Vergleich zu seinem konventionellen Gegenstück erheblich reduziert. Zusätzlich entwickeln wir datenabhängige Korrekturen für abgeschnittene Multiplikatoren, wobei die vorgeschlagenen Architekturen die bestehenden approximativen Multiplikatoren in der Literatur übertreffen.

Die Anwendbarkeit der vorgeschlagenen Methoden und generell approximative Recheneinheiten werden schließlich in modernen Anwendungen untersucht. Die Korrelation zwischen den Fehlern einer einzelnen Einheit und der Genauigkeit des Gesamtsystems wird ebenfalls in den Anwendungen untersucht.

## Acknowledgment

I, personally, consider myself a lucky person. Throughout my life, I have always been destined to meet amazing people. I cannot name all of the people, but I thank anyone who helped me to get to this point. Yet, I would like to name the people most directly responsible for this dissertation becoming a reality.

First and foremost, I would like to thank Prof. Alberto Garcia-Ortiz. I was blessed to be supervised by him during my PhD study. I strongly believe that this work could not be succeeded without his supervision. He is such a phenomenal person who not only improved my research and teaching skills but also impacted on my character and made me a better person. Besides being a professional boss who is strict in the work, he has developed an international team and a genuinely friendly workplace. Alberto is a thoughtful, supportive and diligent person. He loves his job which is the best motivation for his PhD students. I do greatly appreciate all what he has done for me.

Next, I would like to thank Kerstin Janssen, the administrator of ITEM.ids group at university of Bremen. Indeed, I cannot thank you Kerstin with words. You have helped each of us significantly. From the very beginning, by finding a flat for my brother and me, which is out of the scope of your responsibilities, to bringing the very delicious "Grünkohl and Kasseler" for me when I was writing my defense, to the very last one with helping me binding the printed dissertation, I was fortunate to have you as my teammate. You literally made my life much easier in Bremen. Thank you Kerstin, a million.

I could not ask for a better working group and for better colleagues. Among my teammates, I would like to first thank the one who is not only my brother, but also the most supportive friend of mine throughout my life. Amir has been there for me whenever I needed help. In my difficulties, happiness, and sickness, Amir has always been the one I counted on, in whole my life. Clearly, without you I could not easily get to this point. Wanli Yu and Yanqiu Huang, the lovely couple, who have been valuable colleagues and are great friends, helped me a lot during my PhD. Thank you for all your supports and motivations. I am proud of having you two as my friends. Robert Schmidt, it has been a fantastic experience to work with you. Yarib Nevarez, thank you for bringing your positive energy to our group. And more than anybody else, I spent time with Lennart Bamberg. He is an ambitious, determined, genius person. I have learned a lot by working with him. I enjoyed each and every moment with you Lennart, during working hours as well as hanging out with you outside of the institute. I am happy to have you as my friend.

Besides the IDS group, I would like to thank Maike Schröder, Peter Lutzen, Jakob Döring, Andreas Beering, Jochen Rust, and Mingjie Hao, who helped me in different ways. Andreas and Jakob are not only awesome colleagues, but also amazing friends. The collaboration experience with Mingjie and Jochen

was also superb.

I would also like to thank IMS institute of Leibniz university of Hannover, and more specifically, prof. Guillermo Paya-Vaya and Moritz Weissbrich. We collaborated on a DFG project. It was a very convenient and pleasant experience working with you. I would also like to thank Prof. Goerschwin Fey from Hamburg University of Technology (TUHH), and Prof. Karl-Ludwig Krieger from University of Bremen for serving as two of the examiners for this dissertation.

Among all my beloved friends, I would like to thank Freya Gröning and Charlotte Wagner who made me feel at home from the very beginning in Bremen. I do appreciate their presence in my life.

Last but not least, special thanks goes to my family as well as my partner. Without the supports of my parents, Akram and Akbar, I could not attend at university of Bremen to pursue my PhD. The first credit of this dissertation belongs to my parents without any doubt. I owe them until the end of my life, and I am grateful to have their supports. My sister, Elahe, did a lot for me. Elahe has been the most supportive sister I have ever seen. I also thank Shahin Vaziri, my brother-in-law. I never forget your supports specially during my master study. I also would like to thank Stefanie Jahn. Steffi and her family are wonderful people who I consider as my family here in Germany. Thank you Steffi also for your helps with this dissertation. Above all, I am grateful to have Hedieh Farhandi as my partner. She is such an energetic, positive, supportive, thoughtful and sympathetic person. Hedieh, you are not only my partner, but also my best friend to whom I share all my feelings with. I am fortunate to have you in my life. I thank you for all your supports, and more specifically during the last months when I was writing this dissertation. I am happy to have you beside me.

# Table of Contents

| 1 | Intr | oduction and Overview                                  | J  |

|---|------|--------------------------------------------------------|----|

|   | 1.1  | Motivation                                             | 4  |

|   |      | 1.1.1 Approximate computing:                           |    |

|   |      | 1.1.2 Stochastic computing:                            | 4  |

|   | 1.2  | Research Aims and Objectives                           | 5  |

|   |      | 1.2.1 Publications                                     |    |

|   | 1.3  | Dissertation Outline                                   | 8  |

| 2 | Bac  | kground and Previous Works                             | 11 |

|   | 2.1  | Introduction                                           | 11 |

|   | 2.2  | Approximate Adders                                     | 11 |

|   |      | 2.2.1 Approximate Full Adders                          | 13 |

|   |      | 2.2.2 Speculative Adders                               | 14 |

|   |      | 2.2.3 Segmented Adders                                 | 15 |

|   |      | 2.2.4 Speculative Carry Select Adders                  | 16 |

|   | 2.3  | Approximate Multipliers                                | 17 |

|   |      | 2.3.1 Approximation in Generating the Partial Products | 19 |

|   |      | 2.3.2 Approximation in the Partial Product Tree        | 19 |

|   |      | 2.3.3 Approximate Compressors                          | 20 |

|   |      | 2.3.4 Multipliers Derived by Optimization Algorithms   | 22 |

|   | 2.4  | Conclusion                                             | 22 |

| 3 | lder | itification of Problems in State-of-the-art            | 23 |

|   | 3.1  | Introduction                                           | 23 |

|   | 3.2  | Metrics                                                | 26 |

|   | 3.3  | A Fair Comparison of Approximate Adders                | 30 |

|   | 3.4  | A Fair Comparison of Approximate Unsigned Multipliers  | 37 |

|   |      |                                                        |    |

|   | 3.5  | Conclusion                                                    | 41  |

|---|------|---------------------------------------------------------------|-----|

| 4 | Inac | ccurate Adders                                                | 43  |

|   | 4.1  | Introduction                                                  | 43  |

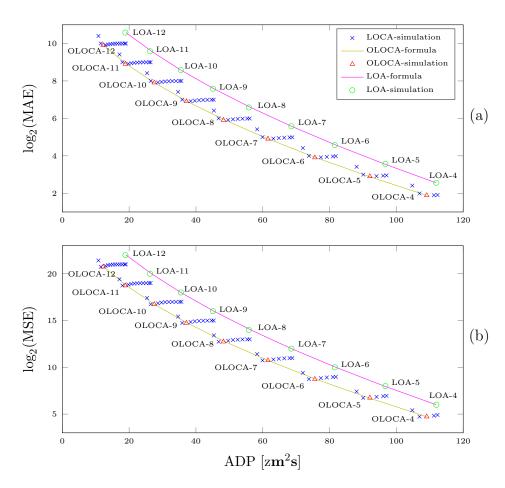

|   | 4.2  | Optimized Lower-part Constant-OR Adder                        | 44  |

|   |      | 4.2.1 Architecture                                            | 45  |

|   |      | 4.2.2 Experimental Results                                    | 54  |

|   | 4.3  | Unified Design Framework and Metrics of Hybrid Approximate    |     |

|   |      | Adders                                                        | 57  |

|   |      | 4.3.1 Hardware modeling                                       | 57  |

|   |      | 4.3.2 Design Methodology                                      | 62  |

|   |      | 4.3.3 Error philosophies of approximate adders                | 63  |

|   |      | 4.3.4 Experimental Results                                    | 64  |

|   | 4.4  | Stochastic Mixed-PR: A Stochastically-Tunable Low-Error Adder | 69  |

|   |      | 4.4.1 Stochastic Analysis                                     | 71  |

|   |      | 4.4.2 Experimental Results                                    | 76  |

|   | 4.5  | Conclusion                                                    | 80  |

| 5 | Inac | ccurate Multipliers                                           | 83  |

|   | 5.1  | Introduction                                                  | 83  |

|   | 5.2  | Truncated Multipliers                                         | 84  |

|   | 5.3  | Constant Correction of Truncated Multipliers                  | 86  |

|   | 5.4  | Data-dependent Correction of Truncated Multipliers            | 87  |

|   | 9    | 5.4.1 1-bit Correction                                        | 88  |

|   |      | 5.4.2 2-bit Correction                                        | 90  |

|   |      | 5.4.3 m-bit Correction                                        | 93  |

|   | 5.5  | A Template for Truncated Multipliers                          | 95  |

|   | 5.6  | Experimental Results                                          |     |

|   | 5.7  | Conclusion                                                    |     |

| 6 | Frrc | or tolerant applications - case studies                       | 107 |

| • | 6.1  | Introduction                                                  |     |

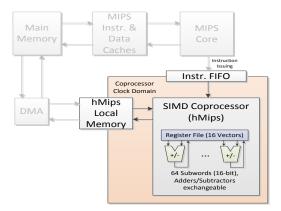

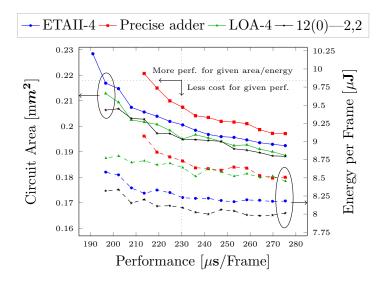

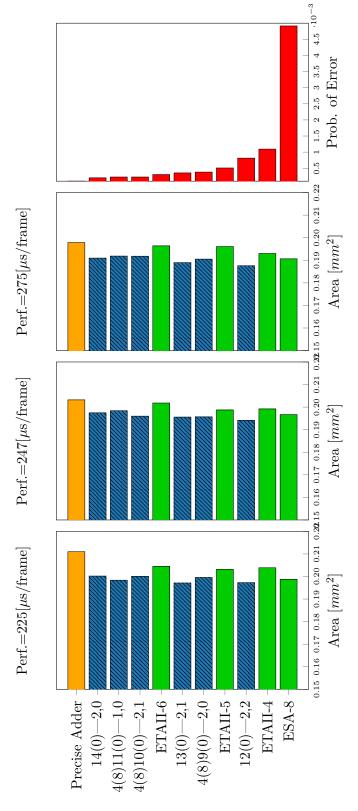

|   | 6.2  | Approximate SIMD Coprocessor: Sobel filter                    |     |

|   | 6.3  | Motion Estimation: Combining Stochastic Communication and     | 100 |

|   | 0.0  | Approximate Computation                                       | 113 |

|   | 6.4  | IoT: Combination of Task Allocation and Approximate Computing |     |

|   | 6.5  | Industrial Wireless Communication System                      |     |

|   | 6.6  | Conclusion                                                    |     |

| 7 | Con  |                                                               | 137 |

# **Specific Mathematical Symbols**

$Pr[x_i]$  probability of  $x_i$  being 1.

$T_{\rm clk}$  period time of the clock determining the pattern duration.

$T_{\rm pd}$  50%–50% propagation delay.

$V_{\rm dd}$  power-supply voltage.

bit-wise logical/Boolean negation.

$\mathbb{E}[X]$  expectation operator for a value discrete variable X.

$\mathbb{N}$  set of natural numbers:  $\{0,1,2,3,\dots\}$ .

$\mu$  average error.

⊕ Boolean Logical exclusive disjunction (XOR) operator.

$\sigma^2$  variance of error.

$\sigma$  standard deviation of error. f frequency equal to  $1/T_{\text{clk}}$ .

|X| the absolute value of variable X.

$\log_2(x)$  binary (base 2) logarithm of x.

$x_1 \mod x_2$  modulo operation for  $x_1$  over  $x_2$  (i.e., the remainder after

the division).

### **Acronyms**

ACA Almost Correct Adder.

ADP Area-Delay Product.

AI Artificial Intelligence.

**ALU** Arithmetic and Logical Unit.

**AND** Logical conjunction.

**ANT** Algorithmic Noise Tolerance.

ASIC Application-Specific Integrated Circuit.

BAM Broken-Array Multiplier.

CAD Computer-Aided Design.

CDF Cumulative Density Function.

CLA Carry Lookahead Adder.

CMOS Complementary Metal-Oxide-Semiconductor.

CPU Central Processing Unit.

CSA Carry-Save Adder.

DAG Directed Acyclic Graph.

**DFG** German Research Foundation.

**DMA** Direct Memory Access.

**DRAM** Dynamic Random-Access Memory.

**DSP** Digital Signal Processing.

**EDA** Electronic Design Automation.

EDP Energy-Delay Product.

ESA Equally Segmented Adder.

ETAII Error Tolerant Adder type II.

ETM Error Tolerant Multiplier.

FA Full Adder.FF Flip-Flop.

FFT Fast Fourier Transform.

FIFO First-In First-Out.

FO4 Fan-Out of 4.

FOS Frequency Over-Scaling.

**FPGA** Field-Programmable Gate Array.

**FSM** Finite State Machine.

GeAr Generic Accuracy-configurable Adder.

**HA** Half Adder.

IC Integrated Circuit.IoT Internet of Things.

ITRS International Technology Roadmap for Semiconductors.

LOA Lower-part OR Adder.

LSB Least Significant Bit.

LSP Lower Significant Partial product.

MAC Multiply-Accumulate Unit.

MAE Mean Absolute Error.

MOSMetal-Oxide-Semiconductor.MOSFETMOS Field-Effect Transistor.MRAEMean Relative Absolute Wrror.

MSB Most Significant Bit.

MSE Mean Squared Error.

**NAND** Logical non-conjunction.

NMSE Normalized Mean Squared Error.

NN Neural Network.

NOR logical non-disjunction.

**OLOCA** Optimized Lower-part OR-Constant Adder.

**OR** logical disjunction.

**PDF** Probability Density Function.

PDK Process Design Kit.

PDP Power-Delay Product.

PDP Power-Delay Product.

PP Partial Product.

PPA Parallel-Prefix Adder.

PPT Partial Product Tree.

PVT Process Voltage Temperature.

RAM Random-Access Memory.

RCA Ripple-Carry Adder.

RF Radio Frequency.

RGB Red-Green-Blue.

RISC Reduced Instruction Set Computer.

ROM Read-Only Memory.

RTL Register-Transfer Level.

Rx Receiver.

SAIF Switching Activity Interchange Format.

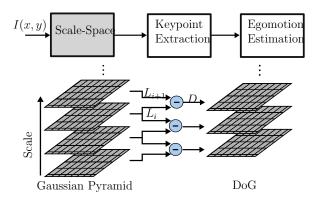

SIFT Scale-Invariant Feature Transform.

SIMD Single Instruction, Multiple Data.

SMSE Saturated Mean Squared Error.

SNR Signal-to-Noise Ratio.

SoC System On Chip.

SPICE Simulation Program with Integrated Circuit Emphasis.

SRAM Static Random Access Memory.

SSIM Structural Similarity Index Measure.

STA Static Timing Analysis.

STD Standard Deviation.

Tx Transmitter.

**UDM** UnderDesigned Multiplier.

VCD Value Change Dump.

VHDL Very high speed integrated circuit Hardware Description

Language.

VLSI Very-Large-Scale Integration.

VOS Voltage Over-Scaling.

XNOR logical exclusive non-disjunction.

XOR Logical exclusive disjunction.

# CHAPTER 1

#### Introduction and Overview

| 1.1 | Motivation                   | 2 |

|-----|------------------------------|---|

| 1.2 | Research Aims and Objectives | 5 |

| 1.3 | Dissertation Outline         | 8 |

Nowadays, a transcendent challenge is growing as the increasing approach to Artificial Intelligence (AI) requires huge amount of data and complex calculations. The new systems demand higher performance and more energy efficiency. General purpose computers and Application-Specific Integrated Circuits (ASICs) are employed to step up the development of these new technologies. However, as technology scales down, it is getting increasingly expensive to ensure exact functionality of digital integrated circuits. The variability of devices and interconnects is increasing dramatically due to intrinsic (e.g., unequal dopant concentrations) and extrinsic (e.g., temperature) variations. Meanwhile, exact or high-precision computation is not always necessary. Applications such as multimedia, machine learning and data mining are inherently error-tolerant and do not require a perfect accuracy in computation. In addition, some errors may compensate each other, or their effects on the final result might be negligible. Therefore, Approximate Computing has emerged as a new technique to tackle the growing concerns by saving energy consumption and increasing the performance of a computer system, with an accepted loss of accuracy [1,2].

#### 1.1 Motivation

As feature size of transistors shrink with the advances in the technology, it becomes more and more expensive for designers and manufacturers to keep transistors functioning deterministic, even under normal operating conditions. The nondeterminism holds back the continuous technology progress, inspired by the Moor's law [3], in the past few decades [4].

Moreover, as transistor counts grow exponentially following Moore's law, the transistor threshold and supply voltages do not scale proportionately, and the power consumption of the additional transistors can no longer be alleviated through circuit-level techniques. As a result, a percentage of transistors of an integrated circuit cannot be powered-on at the nominal operating voltage to mitigate a given thermal design power constraint. The powered-off transistors are called dark silicon [5,6]. Based on the technological data from ITRS and Intel, at the 8nm node, the area of dark silicon escalate over 50% of the chip area [5,7,8]. It brings new unprecedented challenges for the design community. Different design methodologies such as sub/near-threshold design [9–11] and approximate computing [2,12–14] have been studied to address this problem.

Many applications such as computer vision, multimedia, and machine learning do not always require exact and high-precision computations. For instance, the impact of an extent of errors on the output quality of image, video and audio processing is imperceptible for humans. One approach is to exploit the ability of some applications to tolerate errors and deliberately expose the underlying system to the errors. This approach is a new vision with a radical view of the design of hardware systems: a plea for the early targeted identification and development of the faulty properties of hardware during the design phase [1,2]. By matching the statistical hardware error characteristics to the statistical processing requirements of the target application, it is possible to achieve an enormous increase in energy efficiency or performance.

There are two fundamentally different approaches to assess the trade-off between hardware efficiency and precision: Approximate computing [2] and stochastic data processing [1]. With approximate computing, the requirements for an exact implementation of a Boolean function are relaxed; the exact functionality is replaced by an approximated functionality. The approximated functionality is chosen so that it can be implemented more effectively. In contrast, with stochastic data processing, the requirement for correct operation over the entire operating range is reduced. For example, frequency or voltage over-scaling are stochastic techniques which result in timing violation of some paths in the circuit.

Despite the fundamental differences, the key innovation in both approximate and stochastic data processing is that errors are allowed and are considered part of the design; the causes and effects of errors differ, however, and therefore require different design methods. Indeed, it is even possible to combine methods from both approaches, which leads to better results in terms of improving hardware costs as well as accuracy.

#### 1.1.1 Approximate computing:

The idea of approximating a logical functionality is so general that it can be applied to both software [15] and hardware [16]. The history of approximate computing dates back to early 1960s, where it was embraced to develop multiplication and division based on logarithm [17]. In this work, the binary logarithm is determined approximately from the number itself by simple shifting and counting. The next remarkable contributions during the next decades were truncation based approximate designs. In truncated computing units, some Least Significant Bits (LSBs) are pruned resulting in reduction in the circuit complexity. At the same time, the truncation generates errors which appear frequently, albeit when appear they are relatively small. In the case of multipliers, the truncation is applied to the Partial Products (PPs) which results in faster and more energy efficient partial product accumulation stage. Fixed-width multiplier, where the bit-width of input data and the output result are the same, were studied in [18–20]. The concept of approximate computing, afterwards, was applied to adders in [21]. The critical path of an adder is determined by its full carry chain. An exact adder obtains the final carry out and calculates the final results considering all the input bits. However, in real applications, due to the fact that the data distribution is not fully uniform, the effective carry chain of the adder is much shorter for most combinations of inputs. Therefore, a faster adder is developed with a much shorter carry chain which approximates the result. In an n-bit approximate adder, the carry is obtained by its previous k bits where k < n, resulting in a significantly shorter critical path.

In the past decade, approximate adders and multipliers have been in the center of researchers' attention resulting in a plethora of proposed approaches. The notable designs include the the Error Tolerant Multiplier (ETM) [22], Broken-Array Multiplier (BAM) [23], the UnderDesigned Multiplier (UDM) [24], Lower-part OR Adder (LOA) [23], the Equally Segmented Adder (ESA) [25], the Almost Correct Adder (ACA) [26], the Generic Accuracy-configurable Adder (GeAr) [27], Error Tolerant Adder type II (ETAII) [28]. Approximate adders and multipliers have also been generated using evolutionary design approaches [29–33]. Besides, in recent years, the approximate design of Multiply-Accumulate Unit (MAC) is gaining significant attentions [34–36]. The MAC is the core arithmetic computation performed during Neural Network (NN) inference.

On a closer inspection of approximate arithmetic units, current approaches use two philosophies for the error: small errors or unlikely errors. In the first philosophy, approximate units are constructed so that the magnitude of errors is small even if they occur frequently. This is justified by error masking due to intrinsic rounding and noise errors, which is why no significant degradation of the application is to be expected. One example of this group is the LOA [23]. In the second philosophy, errors are constructed so that they rarely occur, even if they are large when they appear. The basic principle is based on the property that an application can survive errors as long as they are rare. An example of this group is the ETAII [28].

#### 1.1.2 Stochastic computing:

Stochastic processing is a promising approach for designing energy-efficient embedded hardware systems. It has been emerged to address the problem of the languishing benefits of technology scaling. Stochastic processing uses the ability of many applications to tolerate a loss of quality in terms of precision of results. In stochastic computing, the requirement for correct operation over the entire operating range is reduced. Traditionally, the aim of the designers is to ensure correct operation of the hardware under all possible Process Voltage Temperature (PVT) variations. However, in stochastic computing, instead of hiding restrictions in hardware implementation behind expensive guardbands, the causal variability of the hardware is specifically revealed. Correspondingly, designers can palliate traditional constraints, which leads to significantly increased processing speed and results in energy benefits [37–42]. Stochastic techniques can be applied on different levels of abstraction including transistor and gate level, as well as Register-Transfer Level (RTL) and architecture level.

The error rate of the error resilient design determines the energy benefits offered by stochastic computing techniques. For example, when the error rate rises sharply with voltage/frequency over-scaling, due to confined scalability, only limited benefits are feasible. In case the error rate increases gradually, the benefits are considerable [37].

The better-than-worst-case strategy is advocated by the researchers to build designs which operate correctly under nominal conditions, and effectively address the challenges of deep sub-micron design [43]. This approach relaxes design constraints on core components, reduces the effects of physical design challenges, and correspondingly, creates opportunities to optimize performance and power characteristics. Razor [44] is an approach to dynamic voltage scaling, based on dynamic detection and correction of circuit timing errors. Employing this capability to tolerate timing errors, a Razor design consolidates self-checking circuits to enable pushing clock frequency and/or supply voltages beyond nominal worst-case levels. Further strategies of better-than-worst-case designs have been reviewed in [45].

Recovery-driven design [38] emphasizes that instead of designing and opti-

mizing hardware systems for correct operations, they should be optimized for a target error rate. Recovery-driven design is developed based on slack distribution. By redistributing timing slack from paths which generate infrequent errors to the critical paths that frequently cause errors, the energy benefits of exploiting error resilience are maximized. As a result, the minimum supply voltage and consequently power consumption are reduced; or the maximum frequency and consequently performance are increased for a target error rate [46].

# 1.2 Research Aims and Objectives

The aim of this dissertation is to identify the problems of the state-of-the-art and address those problems systematically. As mentioned above, a huge number of approximate designs have been proposed in the literature. However, they share a common characteristic: they have been obtained with an ad-hoc and non-systematic methodology. Although there are some exceptions, a majority of the designs aim to achieve an improvement (even if marginal) based on different trade-offs among energy efficiency, silicon area, performance and accuracy. Besides, the evaluations are not systematic. In the one hand, the evaluations are carried out using different synthesis tools and technologies; on the other hand, the metrics employed to quantify the quality of the approximate designs are not methodical. Indeed, the comparisons are mostly deficient. There is lack of systematic and fair comparisons. The basic rules for a fair comparison are often violated in the literature. In a majority of the research works, the proposed design is compared with sub-optimal designs, and the significant baseline designs are missing in the comparisons. Furthermore, even though approximate computing has been proved to be pivotal in the digital Very-Large-Scale Integration (VLSI) design and has received significant attention in the past decade, there is still no comprehensive library which can be used as a reference for comparisons as well as reproducible research.

The aforementioned shortcomings make it difficult to choose a suitable approximate design for a target application. Accordingly, the main objectives of this dissertation are described briefly.

A review and evaluation of existing approximate architectures is presented first in the next chapter. The goal, here, is to classify the approximate adders and multipliers, and review the characteristics of each class. Afterwards, with the overview of the existing approximate architecture, the problem of the state-of-the-art is identified; where fair comparisons of approximate adders and multipliers are performed. A simultaneous comparison of approximate architectures and stochastic exact designs is specifically considered which is believed as a missing point in the existing research works. We believe that approximate computing and stochastic computing have to be studied together, and in some scenarios even be combined to achieve the best trade-off between the

hardware cost and accuracy. In addition, a new metric to quantify the quality of approximate computing units when employed in more realistic scenarios, is presented. The new metric quantify the accuracy of an architecture according to the target application.

A majority of the existing approximate adders have been obtained non-systematic. In order to address this problem, a systematic approximate adder is proposed. The proposed adder is designed by optimizing a developed architectural template for maximum accuracy. Additionally, a comprehensive template for approximate adders is presented along with all the error formulas associated with it. Using the proposed template, various approximate adders can be developed, where the related formulas to the developed approximate adder can be derived from the general formulas. Rather than focusing on approximate computing, the systematic design of inexact adders is expanded to stochastic computing units. A stochastically-tunable low-error adder is proposed afterwards, where frequency over-scaling considered as the stochastic technique to compromise accuracy for energy efficiency.

A data-dependent truncated multiplier is proposed according to the observations from comparison of multipliers. A template for truncated multipliers is also developed, where fixed-width multipliers are also considered as part of the design.

The final goal is to show the applicability of the proposed architectures in real scenarios, where in multiple case-studies the functionality of the designs are evaluated.

#### 1.2.1 Publications

The outcome of the research works for this dissertation, including the collaborative works with our research partners is a list of publications including [47–57]. In the following, a complete list of the related publications are itemized.

#### Journal Articles

- 1. Ayad Dalloo, **Ardalan Najafi**\* and Alberto Garcia-Ortiz, "Systematic Design of an Approximate Adder: The Optimized Lower Part Constant-OR Adder," in IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 26, no. 8, pp. 1595-1599, Aug. 2018, doi: 10.1109/TVLSI.2018.2822278.

- \* All the authors contributed equally to this manuscript.

- 2. Ardalan Najafi, Moritz Weißbrich, Guillermo Payá-Vayá and Alberto Garcia-Ortiz, "Coherent Design of Hybrid Approximate Adders: Unified Design Framework and Metrics," in IEEE Journal on Emerging and Selected Topics in Circuits and Systems, vol. 8, no. 4, pp. 736-745, Dec. 2018, doi: 10.1109/JETCAS.2018.2833284.

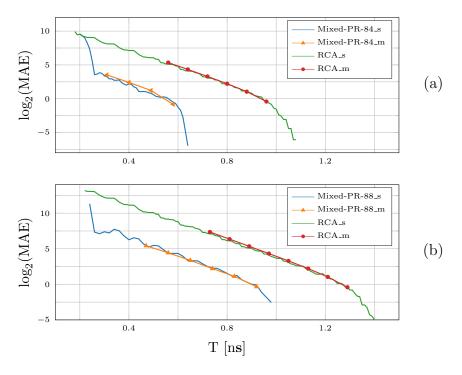

- 3. Ardalan Najafi and Alberto Garcia-Ortiz, "Stochastic Mixed-PR: A Stochastically-Tunable Low-Error Adder," in IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 67, no. 10, pp. 2144-2148, Oct. 2020, doi: 10.1109/TCSII.2019.2953617.

- 4. Wanli Yu, **Ardalan Najafi**, Yanqiu Huang and Aalberto Garcia-Ortiz, "Combination of Task Allocation and Approximate Computing for Fog Architecture based IoT," in IEEE Internet of Things Journal, doi: 10.1109/JIOT.2020.3040892. (Early Access)

- 5. Amir Najafi, **Ardalan Najafi** and Alberto Garcia-Ortiz, "Stochastic Wave-Pipelined On-Chip Interconnect," in IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 67, no. 5, pp. 841-845, May 2020, doi: 10.1109/TCSII.2020.2984194.

- Amir Najafi, Lennart Bamberg, Ardalan Najafi and Alberto Garcia-Ortiz, "Integer-Value Encoding for Approximate On-Chip Communication," in IEEE Access, vol. 7, pp. 179220-179234, 2019, doi: 10.1109/AC-CESS.2019.2959446.

- 7. Moritz Weißbrich, Lukas Gerlach, Holger Blume, **Ardalan Najafi**, Alberto García-Ortiz, Guillermo Payá-Vayá, "FLINT+: A runtime-configurable emulation-based stochastic timing analysis framework," in Integration (Elsevier), Vol. 69, pp. 120-137, 0167-9260, 2019, doi: 10.1016/j.vlsi.2019.01.002.

#### **Conference Proceedings**

- 8. Ardalan Najafi, Moritz Weißbrich, Guillermo Payá Vayá and Alberto Garcia-Ortiz, "A fair comparison of adders in stochastic regime," 2017 27th International Symposium on Power and Timing Modeling, Optimization and Simulation (PATMOS), Thessaloniki, 2017, pp. 1-6, doi: 10.1109/PATMOS.2017.8106990.

- Wanli Yu, Ardalan Najafi, Yarib Nevarez, Yanqiu Huang and Alberto Garcia-Ortiz, "TAAC: Task Allocation Meets Approximate Computing for Internet of Things," 2020 IEEE International Symposium on Circuits and Systems (ISCAS), Sevilla, 2020, pp. 1-5, doi: 10.1109/IS-CAS45731.2020.9180895.

- 10. Mingjie Hao, **Aardalan Najafi**, Alberto García-Ortiz, Ludwig Karsthof, Steffen Paul, Jochen Rust, "Reliability of an Industrial Wireless Communication System using Approximate Units," 2019 29th International

Symposium on Power and Timing Modeling, Optimization and Simulation (PATMOS), Rhodes, Greece, 2019, pp. 87-90, doi: 10.1109/PAT-MOS.2019.8862161.

- 11. Moritz Weißbrich, **Ardalan Najafi**, Alberto Garcia-Ortiz, and Guillermo Paya-Vaya. "ATE-Accuracy Trade-Offs for Approximate Adders and Multipliers in Pipelined Processor Datapaths", Third Workshop on Approximate Computing, 2019, Bremen, Germany (AxC18, www.lirmm.fr/axc18)

- 12. Yizhi Chen, **Ardalan Najafi**, and Alberto Garcia-Ortiz, "On the Effects of Data Distribution on Small-error Approximate Adders," 2020 9th International Conference on Modern Circuits and Systems Technologies (MOCAST), Bremen, Germany, 2020, pp. 1-4, doi: 10.1109/MO-CAST49295.2020.9200260.

- 13. Amir Najafi, Lennart Bamberg, **Ardalan Najafi** and Alberto Garcia-Ortiz, "Misalignment-aware delay modeling of narrow on-chip interconnects considering variability," 2018 7th International Conference on Modern Circuits and Systems Technologies (MOCAST), Thessaloniki, 2018, pp. 1-4, doi: 10.1109/MOCAST.2018.8376593.

- 14. Moritz Weißbrich, Guillermo Payá-Vayá, Lukas Gerlach, Holger Blume, Ardalan Najafi, and Alberto García-Ortiz, "FLINT+: A runtime-configurable emulation-based stochastic timing analysis framework," 2017 27th International Symposium on Power and Timing Modeling, Optimization and Simulation (PATMOS), Thessaloniki, 2017, pp. 1-8, doi: 10.1109/PATMOS.2017.8106956.

- 15. Amir Najafi, Lennart Bamberg, **Ardalan Najafi**, and Alberto Garcia-Ortiz, "Energy modeling of coupled interconnects including intrinsic misalignment effects," 2016 26th International Workshop on Power and Timing Modeling, Optimization and Simulation (PATMOS), Bremen, 2016, pp. 262-267, doi: 10.1109/PATMOS.2016.7833697.

#### 1.3 Dissertation Outline

This dissertation is organized into 7 chapters. The review of the existing approximate architectures is presented following to the introduction in Chapter 2. The chapter is divided into two main sections where approximate adders and approximate multipliers are classified and the prominent existing architectures are highlighted. Fair comparisons of approximate adders and multipliers are provided in Chapter 3. In this chapter, first, the problems of the state-of-the-art are discussed. Subsequently, a new metric is proposed for the evaluation of the accuracy of approximate computing unit considering a target

application. In Chapter 4, the proposed inaccurate adders are discussed. In the first Section of this chapter, a low-power optimized approximate adder is proposed. The proposed adder is designed systematically from a developed template for small-error approximate adders. In section 4.3, hybrid approximate adders are discussed based on the proposed unified design framework. A comprehensive template for approximate adders is proposed in this section. Afterwards, in section 4.4, the error behaviour of exact adders in stochastic regime is mathematically analyzed, where accordingly, a stochastic mixed adder is proposed. Truncated multipliers with data-dependent correction are subsequently proposed in Chapter 5. A template for truncated multipliers along with two correction strategies are presented in this chapter. In Chapter 6, the applicability of the proposed approximate architectures are evaluated in multiple case-studies. Finally, Chapter 7 concludes this dissertation.

# CHAPTER 2

# Background and Previous Works

| 2.1 | Introduction            | 11 |

|-----|-------------------------|----|

| 2.2 | Approximate Adders      | 11 |

| 2.3 | Approximate Multipliers | 17 |

| 2.4 | Conclusion              | 22 |

### 2.1 Introduction

A huge number of approximate computing units have been proposed in the literature. Although approximate adders have been studied more than other approximate computing units, the attention of the researchers have been increasingly attracted to approximate multipliers in the recent years. In this chapter, the goal is to review the state-of-the-art and different approximation methodologies. The comparison of the approximate architectures, however, is left for the next chapter where we discuss the problems in the state-of-the-art. As a result, here, relevant approximate adders and approximate multipliers are classified and briefly reviewed. First, in the next section, different approximate adders with different design strategies are studied. Then, in section 2.3, different classes of approximate multipliers are investigated.

# 2.2 Approximate Adders

Addition of two binary numbers is one of the most basic arithmetic circuits in a digital computer. Adders, as one of the key components of arithmetic circuits, have attracted lots of researchers' attention in the field of approximate computing. The most basic and fundamental adder architecture is the Ripple-Carry Adder (RCA). An n-bit RCA is constructed by n Full Adders (FAs), where the input carry of each full adder is fed by the output carry of the previous full adder; resulting in a long propagated carry chain. Correspondingly, the delay and silicon area of the RCA increase proportionally with n (O(n)). Another basic adder architecture is the Carry Lookahead Adder (CLA). In an n-bit CLA, there are n units which work in parallel to produce the generate  $(g_i = a_i b_i)$  and propagate signals  $(p_i = a_i + b_i)$ . The generate and propagate signals are then employed to generate the look-ahead carries. The delay of CLA is logarithmic in n  $(O(\log(n)))$  which is much shorter than delay of RCA. However, a CLA requires a larger Circuit area  $(O(n\log(n)))$ , resulting in a higher power dissipation.

High speed adders are based on well established parallel-prefix architectures [58], including Brent-Kung [59], Kogge-Stone [60], Sklansky [61], Han-Carlson [62], etc. A Parallel-Prefix Adder (PPA) formulates a binary addition using three stages: pre-processing, prefix-processing and post-processing. The pre-processing stage computes generate  $g_i$  and propagate  $p_i$  signals using bit-wise operations:

$$g_i = a_i b_i, (2.1)$$

$$p_i = a_i \oplus b_i, \tag{2.2}$$

where a and b are the inputs, and i denotes the bit position. The prefix-processing stage exploits the prefix operator, to speed-up carry computation. The prefix-processing stage is core of the parallel-prefix adders. Since the prefix operator is associative and idempotent, the individual operations can be carried out in any order. This has resulted to emergence of diverse existing parallel-prefix architectures.

The post-processing stage computes the sum bit  $s_i$  as follows:

$$s_i = p_i \oplus c_{i-1} \tag{2.3}$$

where  $c_{-1} = C_{in}$  and  $c_i = g_{[i:0]}$ .

Various approximation schemes have been proposed in order to reduce the critical path and hardware complexity of exact adders. The concept behind all the approximate adders is to break the carry propagation chain and consequently perform the addition faster than exact adders. A conventional scheme to cut the carry propagation chain and reduce the delay of the critical path as well as the power dissipation is to use approximate full adders to implement the LSBs of an adder. This class of approximate adders are known as approximate full adders [16, 23, 63–66]. Another methodology is based on a speculative operation [21, 26, 67]. In a speculative adder, each sum bit is calculated using

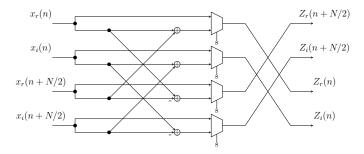

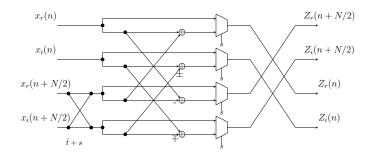

its previous k LSBs, where k is less than n (k<n). Because of the fact that the carry chain is shorter than n, a speculative adder is faster than a conventional adder. A segmented adder is composed by several smaller sub-adders working in parallel [25,27,28,68,69]. Accordingly, the carry propagation chain is reduced into shorter segments. The segmentation technique is used in [70–74] with a similar concept. However, the carry input of each sub-adder block is selected with an altered strategy. Correspondingly, this class of approximate adders is called speculative carry selection adder. Therefore, the approximate adders are divided into four categories, which are briefly summarized below.

#### 2.2.1 Approximate Full Adders

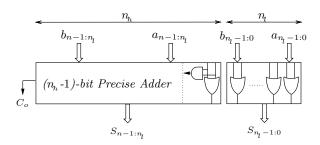

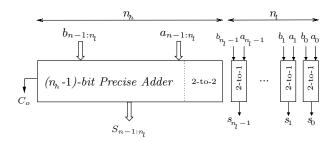

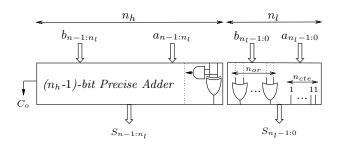

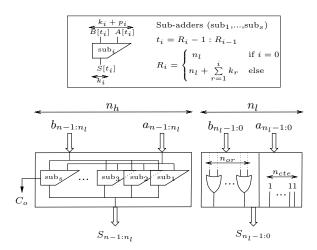

In this class of approximate adders, the adder is divided into two sub-adders. The higher significant sub-adder is an exact adder, while the lower significant is constructed employing approximate full adders. This class includes a simple approach of truncation. A truncated adder is an adder which its output LSBs are replaced with constant bits. In the case where the LSBs are replaced with constant ones we call it TruncOne and if the LSBs are replaced with constant zeros, it is called TruncZero in this dissertation. The Lower-part OR Adder (LOA) [23] is the most well-known design in this class. It divides an n-bit adder into two sub-adders. While the higher significant sub-adder is an  $(n - n_{or})$ -bit exact adder, the lower part sub-adder is simply constructed by  $n_{or}$  number of OR gates. To generate the Carry-in signal for the higher significant exact sub-adder, an extra AND gate is used which ANDs the most significant input bits of the lower significant sub-adder. The critical path delay of LOA then depends on the size of the exact sub-adder. The other figures of merit are also dependent on the exact sub-adder architecture. It is obvious that using different architectures as the sub-adder in LOA results in different performances as well as in different silicon areas and/or power consumptions. Fig. 2.1 shows the topology of a LOA. As can be seen, an n-bit LOA exploits a regular smaller precise adder that computes the precise values of the  $(n_h - 1)$  most significant bits of the result along with OR gates that approximate the  $n_{or}$  least significant result bits by applying bit-wise OR to the respective input bits.

In addition, the approximate XOR/XNOR-based adders proposed in [63] is also classified as approximate full adders. The approximate adders proposed in [63] are based on using XOR and XNOR gates with multiplexers implemented by pass transistors. In the design of the approximate XOR/XNOR-based full adders, some of the transistors required in the accurate adder design have been removed to achieve lower logic complexity. In a similar approach, in [16], several approximate mirror adder designs are proposed by removing some of the transistors. They reported up to 60% power saving by approximating LSBs with this approach. In [66] majority logic based approximate full adders are proposed, and in [65] a proposed majority gate is employed to design an

Fig. 2.1: Hardware architecture of the Lower-part OR Adder (LOA)

accuracy-configurable full adder cell. The above-mentioned designs except LOA, require customized layout. As a result, for the comparison, LOA is considered for our evaluations. In addition, the truncated adders are considered as baseline designs. Since the approximate full adders approximate the LSBs, they generate frequent errors. However, the errors generated by this class of adders are small in magnitude.

#### 2.2.2 Speculative Adders

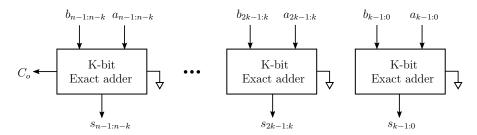

In a speculative adder, each sum bit is calculated using its previous k LSBs, where k is less than n (k<n). The Almost Correct Adder (ACA) [26], is the most applicable adder of this class designed based on [21]. The rationale for ACA design is that the probability of having k-2 Consecutive propagate bits is low enough to produce correct results for majority of the input combinations. However, for large k, the expected improvement in the speed is not achieved with ACA compared with an exact adder; and with small k, the accuracy does not correlate with the name of the adder. In addition, the area overhead of having multiple sub-adders is considerable in comparison with an exact adder. The ACA design can be seen in Fig. 2.2.

Fig. 2.2: Almost Correct Adder (ACA), k is the number of previous LSBs used for the calculation of the sum bits.

#### 2.2.3 Segmented Adders

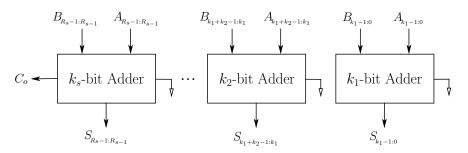

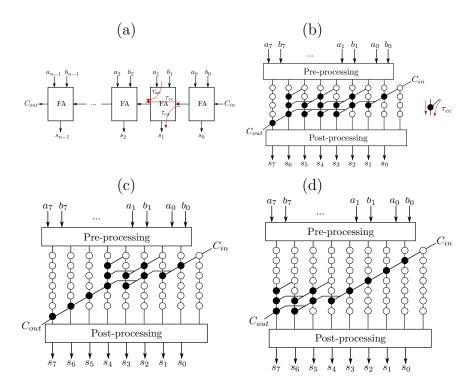

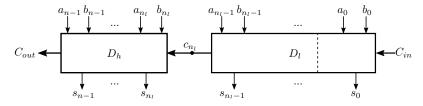

A segmented adder divides an n-bit adder into a number of smaller sub-adders which operate in parallel with fixed carry inputs. Let  $\mathbb{K} = \{k_1, k_2, \dots, k_s\}$  denote a vector including size of sub-adders, where s is the number of sub-adders. In Fig. 2.3, a segmented adder divided into s sub-adders is shown, where  $k_1$  is the size of the first (the lowest significant) sub-adder,  $k_2$  is the size of the second sub-adder, and so on.

The Equal Segmentation Adder (ESA) is a type of segmented adders with equally sized sub-adders, i.e.  $k_1 = k_2 = \cdots = k_s$ . Conventionally, ESA is considered as an n-bit adder divided into  $\frac{n-k_1}{k}$  equally sized sub-adders in addition to the lowest significant sub-adder with the size  $k_1$  where k is the size of equal sub-adders and  $k_1 < k$ . Accordingly, the delay and the area of an ESA is dependent to the structure of the sub-adders.

Fig. 2.3: The structure of the Segmented Adder divided into s sub-adders with arbitrary sizes, where  $R_x = \sum_{i=1}^x k_i$ .

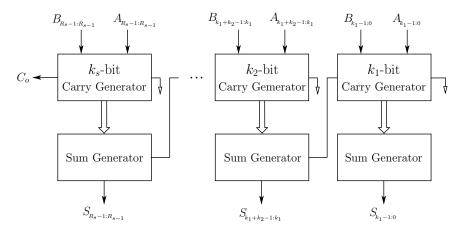

ETAII, proposed in [28], is another approximate adder based on segmented adders. It splits the entire carry propagation path into a number of short paths and completes the carry propagations in these short paths concurrently. Let us consider the general case of the ETAII with arbitrary block sizes. As depicted in Fig. 2.4, the architecture of ETAII is divided into smaller blocks. Each block has an arbitrary number of bits and, different from ESA, consists of two separate circuitries - Carry Generator and Sum Generator. As the name implies, the Carry Generator creates the carry-out signal. It does not take the carry signal from the previous block. The Sum Generator, however, takes the carry-in signal from the previous block to generate its sum output bits. Consequently, the carry propagation only exists between two neighboring blocks instead of lying along the entire adder structure [28]. Conventionally, ETAII is divided into  $\frac{n-k_1}{k}$  equally sized blocks, in addition to the lowest significant block with the size  $k_1$ . Although the circuit complexity of ETAII is similar to ESA (due to the fact that sub-adders in ESA consist both carry and sum generators), considering

parallel prefix adder as the internal sub-adders, ETAII has one extra stage in its prefix structure which exacerbates its speed.

Fig. 2.4: The structure of the ETAII divided into s sub-blocks with arbitrary sizes, where  $R_x = \sum_{i=1}^x k_i$  .

A low latency generic accuracy configurable (GeAr) adder [27] is a generalized design which employs the concept of segmented adders. It uses multiple sub-adder units of equal length to provide a wide-range of accuracy configurability and variable approximation modes. The GeAr provides a higher number of potential configurations compared to state-of-the-art, and provides a template which enabling a high degree of design flexibility and trade-off between performance and output quality.

The error behaviour of segmented adders is completely different from approximate full adders. The segmented adders, due to the method which they cut the carry chain, make big infrequent errors.

### 2.2.4 Speculative Carry Select Adders

A speculative carry select adder is an approximate adder divided into sub-adders where the carry inputs of the sub-adders are selected with different methodologies. The speculative carry selection adder (SCSA) [71] is divided into  $\lceil \frac{n}{k} \rceil$  blocks called "window". Each window adder consists of two k-bit exact adders where the input carry of  $Adder_0$  is connected to zero and the input carry of  $Adder_1$  is connected to One. The sum result of each window adder is selected with a multiplexer which its select input is connected to the output carry of  $Adder_0$  of the previous (lower significant) window adder.

The approximate architecture proposed in [72] uses the generate signals for carry speculation. Here, the carry selection depends on the propagate signal of each sub-adder. In case the propagate signal is one, the carry-in of the block is

the most significant generate signal of the previous block; and if the propagate signal is zero, the carry-in of the block is the carry-out of the previous carry generator block.

The Carry Cut-Back Adder (CCBA) [74] is composed of sub-adder blocks where multiplexers are inserted in order to cut the carry chain to reduce the critical path delay. The cut multiplexes the real carry with a carry speculated from a much shorter chain. The decision to cut the chain is taken in the carry propagate block (PROP) which monitors a group of carry stages and generates the cut signal if those are all in propagate states. The accuracy of the CCBA adder depends on how large is the bit-width between the propagate block and the cut.

The speculative carry select adders usually provide a high accurate results. However, the high circuit overheads of those adders make them less interesting than the approximate full adders and segmented adders.

## 2.3 Approximate Multipliers

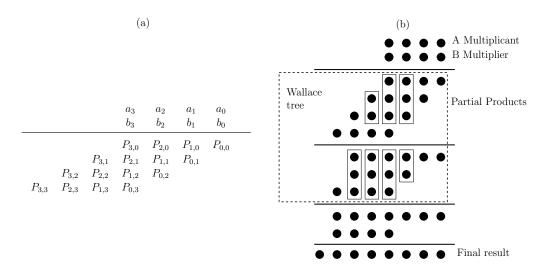

Multiplication is the main operation in many signal processing applications. Multipliers are the most power-hungry units of Arithmetic and Logical Units (ALUs). In most of the DSP applications, multipliers are part of the critical path and hence determine the speed of the system. A multiplier consists of three stages: 1) partial product generation, 2) partial product reduction (accumulation), 3) a final addition, as shown if Fig. 2.5(b).

Fig. 2.5: (a) The partial product tree,  $P_{i,j} = a_i b_j$ . (b) A 4×4 Wallace multiplier.

Considering A and B as the inputs of a multiplier, partial products of the multiplier  $P_{i,j}$  are the products of the two bits  $(a_i \text{ and } b_i)$  generated by AND

gates (i.e.  $P_{i,j} = a_i b_j$ ), where i and j are the bit position of inputs a and b, respectively. Since in binary multiplication  $b_i$  is in  $\{0, 1\}$ , each row of the partial product tree can be either 0 or  $a \times 2^j$  which is the shifted version of input "a". Because of this fact, the multiplication sometimes is considered as the combination of shift and add operations.

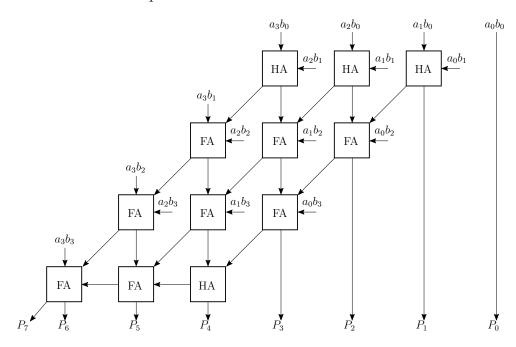

The frequently used partial product reduction strategies are the carry-save adder array, Wallace and Dadda trees [75,76]. A carry save adder array (Fig. 2.6) employs a row of binary FAs to reduce three numbers to two numbers. The carry and sum signals produced in each row are fed to the next row of the FAs. Since the adders which are in a column work in a serial order, the partial product reduction with carry save adders is relatively slow. The multipliers using carry save adder array as the partial product reduction stage are called Array multipliers. The Wallace and Dadda trees [77,78] employ (3,2) and (2,2) counters (i.e. Full Adder (FA) and Half Adder (HA), respectively) at each level of partial product accumulation to achieve required reduction. Dadda multipliers use a minimal number of FAs and HAs at each level, while in Wallace trees, the number of operands are reduced at the earliest possibility. In other words, if there are h dots in a column,  $\lceil \frac{h}{3} \rceil$  FAs are immediately applied to that column. This results in minimizing the overall delay by making the final addition as small as possible.

Fig. 2.6: The structure of partial product reduction of a  $4\times4$  unsigned array multiplier.

The approximate multipliers can be classified in four main classes. The

approximation in generating the partial products is the first class of approximate multipliers [24]. Another class of approximate multipliers designs a multiplier by approximating the partial product tree [22,23,79–82]. This class of multipliers include the conventional truncated multipliers. The third class of approximate multipliers employs approximate blocks for accumulation of the partial products. In [83], an approximate multiplier with error correction is proposed where approximate counters are used for the reduction of the partial products. There are additionally a huge number of designs in the literature where approximate compressors are employed to accumulate the partial products of the multipliers [84–90]. Approximate multipliers can also be classified as the units developed using evolutionary design approaches [29–33].

#### 2.3.1 Approximation in Generating the Partial Products

The most straightforward approach of this class is to utilize smaller approximate multipliers to construct larger multipliers [24,91] which results in approximated partial products. In [24], the proposed underdesigned multiplier employs an approximate  $2\times2$  multiplier. The approximate  $2\times2$  multiplier is designed to make error only when both the inputs are one (i.e. "11"). In this case, the multiplier output is "111" instead of the precise result of "1001", saving one output bit. Consequently, considering a uniform distribution, where each input bit has 50% probability to be 0 or 1, the error rate of the  $2\times2$  approximate multiplier is  $\frac{1}{16}$ . The error introduced by this approximate multiplier generates approximate partial products, while the accumulation of the partial products is still performed precise.

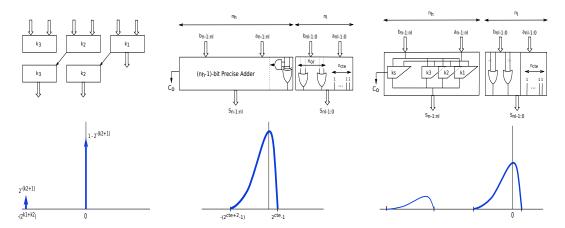

## 2.3.2 Approximation in the Partial Product Tree

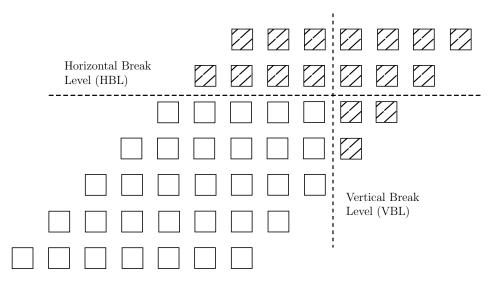

The simplest approach in this methodology is input truncation where k-bit LSBs of the input operands are pruned. In fact, the multiplication is performed for the Most Significant Bits (MSBs) of the operands. This approach results in a relatively high level of inaccuracy. Conventional truncated multipliers are the eminent architectures of this class of approximate multipliers. A truncated multiplier (TruncM) pruns the k LSBs (k least significant columns) of the partial products resulting the k LSBs of the output of the multiplier in constant zeros. Removing the partial products of a multiplier not only reduces the silicon area due to the removal of AND gates, but also scales the speed of the multiplier up as a result of cutting the critical path. Moreover, the area reduction benefits is twofold since the reduced size partial products require lesser hardware to be accumulated. Broken-Array Multiplier (BAM) [23] is a type of truncated multipliers which has a structure similar to an array multiplier. The BAM omits the Carry-Save Adder (CSA) cells horizontally and vertically which lead to a smaller and faster circuit while provides inaccurate results. As shown in Fig. 2.7 the number and position of the omitted cells (that are hatched) depend

on two parameters: Horizontal Break Level (HBL) and Vertical Break Level (VBL). The BAM technique results in a same accuracy when applied to other multipliers such as Wallace-tree. The Error-Tolerant Multiplier (ETM) [22] splits a multiplier into LSBs and MSBs. A control unit checks the product of the MSBs (using NOR gates). If the product of MSBs is zero, then the LSBs are multiplied normally. But if the product of the MSBs is nonzero, a non-multiplication block is used for the the LSBs [22].

Fig. 2.7: The structure of a  $7 \times 7$  Broken Array Multiplier (BAM). The hatched carry-save adders are the omitted cells (Horizontally and/or Vertically).

## 2.3.3 Approximate Compressors

In the design of a fast multiplier, compressors have been widely used to speed up the partial product reduction tree and decrease power dissipation [92–97].

Two approximate compressors are proposed in [84] and then used for the partial product accumulation of a Dadda multiplier. These approximate compressors are designed by simplifying the outputs of the compressor and thereby decreasing the transistor count of the compressors. In [87], a simple but novel idea is proposed to design approximate compressors. In addition, an algorithm to exploit the designed approximate compressors in the partial product reduction stage is presented. The compressors designed in [87] approximate the arithmetic sum. For most of the input combinations, they compute the exact value resulting in a low average error. The outputs of the proposed approximate compressors have the same weight as of the inputs and they do not produce carry outputs, which is the difference from conventional compressors where the weight of the carry output is two times the weight of the inputs.

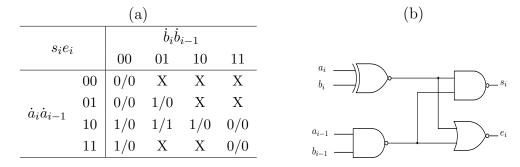

In [98], a new approximate adder cell is proposed. The adder operates on a set of pre-processed inputs. This input pre-processing is done considering the interchangeability of the input bits with the same weights. In the input pre-processing stage, the rule is to swap  $a_i$  and  $b_i$  when  $b_i > a_i$ , otherwise the inputs are kept untouched. By doing so, more 1's are expected in A and more 0's are expected in B. As a result, the pre-processed inputs can be calculated using the following equations:

$$\dot{a}_i = a_i + b_i,

\dot{b}_i = a_i b_i.$$

(2.4)

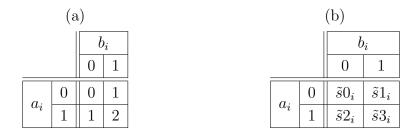

The Eq. (2.4) corresponds to the propagate and generate signals used in a parallel prefix adders. The proposed adder can process data in parallel by cutting the carry propagation chain. A carry signal is produced in the proposed adder only by the generate signal (i.e.,  $a_i = b_i = 1$ ), which based on the pre-processed inputs, it corresponds to when  $\dot{b}_i = 1$ . In addition, the produced carry can only be propagated to the next higher bit. The truth table of the approximate adder cell is tabulated in Fig. 2.8(a).

Fig. 2.8: (a) Truth table of the approximate adder cell proposed in [98]. 'X' represents the combinations which are not possible to occur due to the input pre-processing; (b) approximate adder cell of [98].

The idea of [98] is extended in [99] where besides using the approximate adder cell of Fig. 2.8(b), to achieve further improvement in area and power consumption of the multiplier, truncation is applied to the partial products tree. Depending on the error recovery circuit, the multipliers are called AM1 for the error recovery with OR gates, and AM2 when error recovery circuit employs OR gates and the approximate adder cell of Fig. 2.8(b). The truncated version of these adders are called TAM1 and TAM2, respectively.

#### 2.3.4 Multipliers Derived by Optimization Algorithms

Another approach to design approximate computing units is optimization algorithms such as genetic algorithm [29–33]. EvoApprox library [33] is developed based on conventional adder and multiplier designs. The method used to obtain the library follows the the evolutionary approach introduced in [32]. The methodology is a general-purpose approach to develop approximate combinational circuits based on a multi-objective Cartesian genetic programming. It represents candidate circuits as directed acyclic graphs and develops a set of approximate circuits along a Pareto front by simultaneously optimizing delay, power consumption and accuracy of the approximate unit.

## 2.4 Conclusion

In this chapter, relevant approximate adders and multipliers have been reviewed. An extensive comparison of these architectures are presented in the next chapter. In general, the appoximate full adders, due to applying the approximation to the LSBs, generate small errors but with a high probability. Segmented adders, on the other hand, produce large errors with low probability. In regards to multipliers, applying approximation in the generating the partial products and also in the partial product tree by truncation are effective strategies to reduce the hardware cost. However, the truncation of the partial products results in a higher accuracy than truncating the inputs operands. The multipliers which use approximate compressors in their structures provide the higher accuracy with the cost of higher energy consumption as well as silicon area.

The existing research works optimize an approximate computing unit for different trade-offs among accuracy, silicon area, energy efficiency and performance. Although in each of those designs marginal improvements might have been achieved, due to inconsistency in the error analyses and circuit characterisites, it is challenging to choose a proper architecture for a desired application. In the next chapter, we study the problems in the state-of-the-art in detail and we discuss our approaches to address those problems.

# CHAPTER 3

# Identification of Problems in State-of-the-art

| 3.1 | Introduction                                          | 23         |

|-----|-------------------------------------------------------|------------|

| 3.2 | Metrics                                               | <b>26</b>  |

| 3.3 | A Fair Comparison of Approximate Adders               | <b>3</b> 0 |

| 3.4 | A Fair Comparison of Approximate Unsigned Multipliers | 37         |

| 3.5 | Conclusion                                            | 41         |

## 3.1 Introduction

The languishing benefits of technology scaling has pushed the designers to look for new energy efficient strategies. One approach is approximate computing which has attracted lots of researchers' attention. A vast amount of time and resources of the research companies have been dedicated to approximate-computing-related projects. Correspondingly, a prodigious number of approximate designs have been proposed in the literature. However, it is still difficult to choose a suitable approximate design for a target application. Indeed, there are four fundamental problems which are aimed to be addressed in this dissertation. These problems are listed below:

1. Systematic design approaches: The existing approximate designs in the literature share a common characteristic: they have been obtained with an ad-hoc and non-systematic methodology. Although there are some exceptions (like GeAr adder which is based on the concept of a template), a majority of the designs aim to achieve an improvement based on different trade-offs among energy efficiency, silicon area, performance and accuracy. Our approach, however, is to study the approximate architectures systematically. Rather than improving any existing architecture for a target application or for a specific trade-off, we aim to characterize the error behaviours of the approximate architectures. Afterwards, based on these understandings, architectural templates are developed. Finally, optimized architectures can be obtained from the templates. The promising architectures obtained with our approaches are detailed in Chapter 4 and Chapter 5.

2. Fair comparison: As mentioned above, the interest of stochastic and approximate processing has resulted in a huge number of publications and contributions; each work claiming a superior functionality over the others. The comparisons among the alternatives, however, are not always systematic and fair. On the one hand, different synthesis tools and technologies are employed for the evaluations; on the other hand, the metrics employed to quantify the quality of the approximate designs are not methodical. There is also lack of systematic studies comparing approximate and stochastic architectures. Indeed, the comparisons are mostly deficient. The rules for a fair comparison are often violated in the literature. For example, the selection of an approximate architecture is strongly influenced by the timing constraints of the hardware [48]. The design constraints determine the internal structure of the unit (in case of adders for example, sequential structure with linear cost, parallel-prefix structure with a logarithmic cost, etc.), which determines the reduction in cost achieved by the approximate units. With relaxed timing constraints, an exact adder is implemented with a ripple-carry structure and an ESA almost decreases the delay by a factor of two. With more stringent timing constraints, an exact adder is implemented with a parallel-prefix architecture, where the delay increases as  $\lceil \log_2(n) \rceil$  and the use of an ESA is just marginally reducing the delay. In this case, non-equally segmented sub-adders may be preferable. The effects of the internal adder architecture have been studied in [48]; it illustrates the potentials for non-equally segmented approximate adders which have been disregarded in the literature. In majority of the research works, the proposed design is compared with sub-optimal designs, and the significant baseline designs are missing in the comparisons. For a fair comparison, it is vital to consider all the best possible counterparts. This simple fact has often been violated in the literature, and even in the review articles, which can be misleading for the research community. The aforementioned shortcomings make it difficult to choose a suitable approximate design

for a target application. In this chapter, a fair comparison of adders as well as multipliers are presented and discussed.

- 3. Reproducible research: Reproducible research is an important factor to accelerate advances in any research domain. Despite the fact that approximate computing has received significant attentions, in the digital VLSI design community, in the past decade, there is still no comprehensive library which can be used as a reference for comparisons as well as reproducible research. Indeed, lack of the library of a comprehensive approximate computing unit has slowed down the research in this domain. In conjunction with this dissertation, we have developed an open-source repository where the Very high speed integrated circuit Hardware Description Language (VHDL) codes of the approximate computing units and the golden references are stored. The comparison of approximate computing units can be accessed there for different figures of merit. In addition, the users can add their own designs in the repository. This way, not only the researchers in this domain can access to the code and descriptions of the existing architectures, but also they can evaluate and compare their own architectures with the existing ones on the developed platform. Due to the fact that the architectures are classified and also categorized based on their entities, the fair comparison is ensured using the developed platform. Above all, this way the comparisons are reproducible.

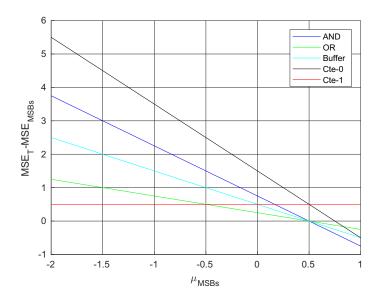

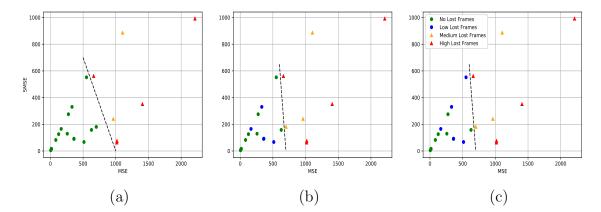

- 4. Metrics: A closer investigation into the variety of approximate units shows that the current approaches use two philosophies for the error: a) small errors or b) unlikely errors. In the first philosophy, the errors of the approximate unit are engineered to be small in magnitude, even if they are frequent. The rationale is that those errors are masked by the intrinsic truncation and noise error of the system, and therefore they do not degrade considerably the quality of the application. Examples of this philosophy are the LOA [23] and truncated adders and multipliers. In the second philosophy, the errors are engineered to appear infrequently, even if they are large when they appear. The rationale is that the application can overcome errors if they are sporadic. Examples of this philosophy are the ACA [68], the GeAr [27], the ETAII [28] and the ESA [25].

A key problem when considering simultaneously the two philosophies is the quantification of the errors. The authors working with the small errors philosophy tend to prefer error metrics as the standard deviation, or the mean average error that measure the average magnitude of the errors. This metric, however, strongly penalizes large infrequent errors. The authors working with the infrequent error philosophy tend to favor metrics as the average number of errors which quantify the error probability; however, this metric strongly penalizes architectures with small errors. In a real scenario, the two effects have to be considered in a single metric, but it is not possible with the current approaches.

In the rest of this chapter, first, a new metric to quantify the quality of approximate computing units when employed in real applications, is proposed. Afterwards, fair comparisons for existing approximate adders and multipliers for different trade-offs are presented and discussed.

#### 3.2 Metrics

The error is defined as the difference between approximate and accurate output results of the computing unit:

$$\varepsilon = \tilde{Y} - Y,\tag{3.1}$$

where  $\tilde{Y}$  is the approximate (erroneous) output of the unit and Y is the accurate result. It is a random variable that can be characterized by its probability density function (i.e.  $Pr[\varepsilon_j]$ ). However, from the perspective of an automated design framework, it is more convenient to use an error metric (a single number) to quantify the importance of the error. Several metrics have been proposed; among them, the most common ones are the Average Error ( $\mu$ ), the average number of errors (PE), the Standard Deviation (STD or  $\sigma$ ), the Mean Squared Error (MSE), the Mean Absolute Error (MAE), and the Mean Relative Absolute Error (MRAE). In the literature (e.g. [100]) the Error Distance and the Mean Error Distance (MED) are used to evaluate the arithmetic performance of approximate computing units. These metrics are actually the absolute error and the MAE, respectively. References [101,102] use MED and error rate (similar to PE), while references [103–105] use relative error metrics. In summary, the most common metrics are defined as follows:

$$PE = \mathbb{E}[\delta(\varepsilon)] = \sum_{j} Pr[\varepsilon_{j}],$$

(3.2)

$$\mu = \mathbb{E}[\varepsilon] = \sum_{j} \varepsilon_{j} Pr[\varepsilon_{j}] , \qquad (3.3)$$

$$\sigma = \sqrt{\mathbb{E}[(\varepsilon - \mu)^2]} = \sqrt{\sum_{j} (\varepsilon_j - \mu)^2 Pr[\varepsilon_j]} , \qquad (3.4)$$

$$MSE = \mathbb{E}\left[\varepsilon^2\right] = \mu^2 + \sigma^2 , \qquad (3.5)$$

$$MAE = \mathbb{E}[|\varepsilon|] = \sum_{j} |\varepsilon_{j}| Pr[\varepsilon_{j}] ,$$

(3.6)

$$MRAE = \mathbb{E}[|\varepsilon|] = \sum_{j} \left| \frac{\varepsilon_{j}}{y_{j}} \right| Pr[\varepsilon_{j}] ,$$

(3.7)

where  $\mathbb{E}$  is the expectation operator. It should be mentioned that it is also common to employ the normalized version of the previous metrics.

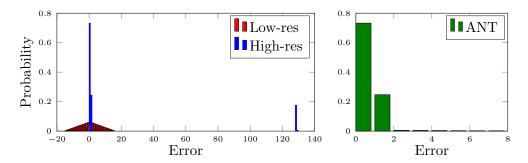

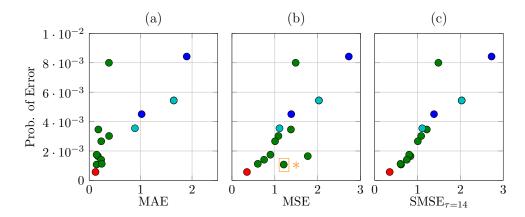

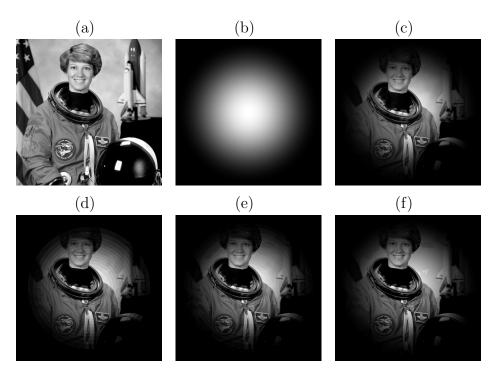

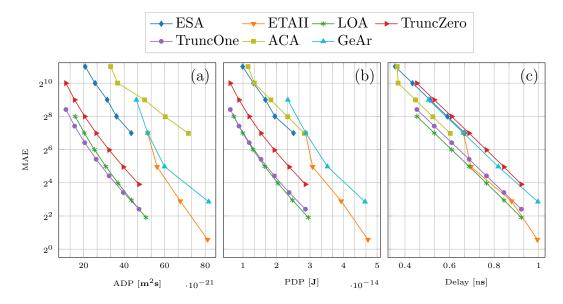

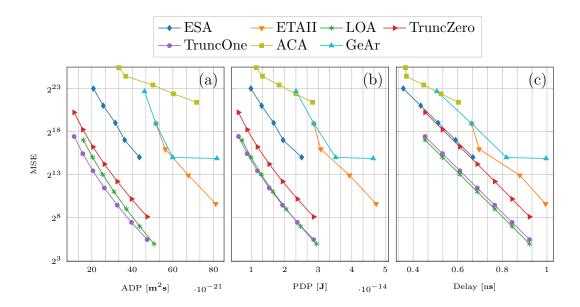

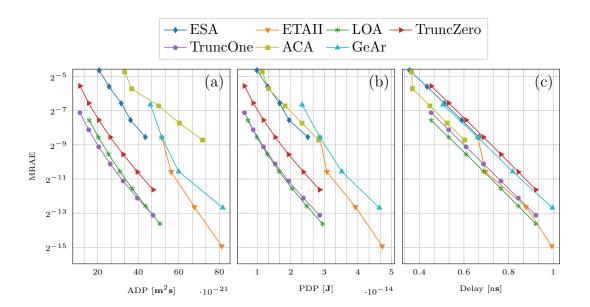

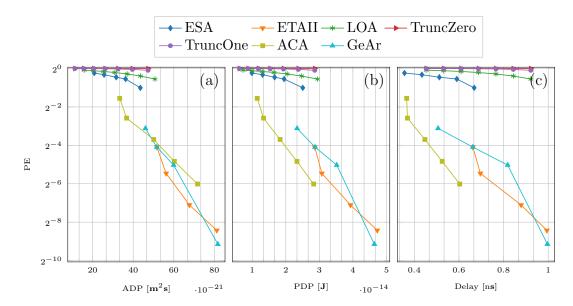

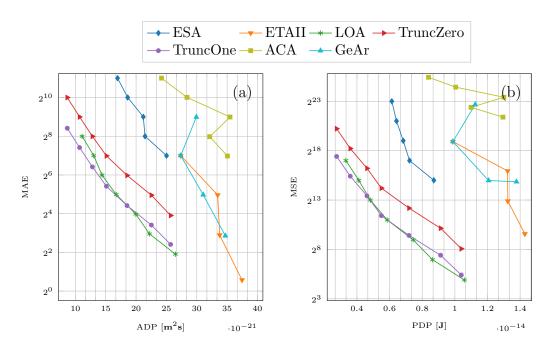

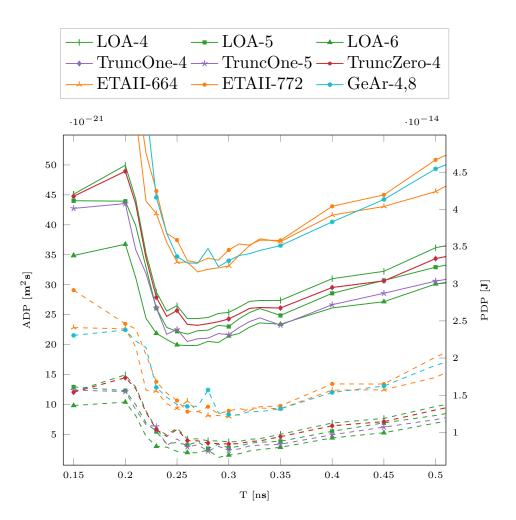

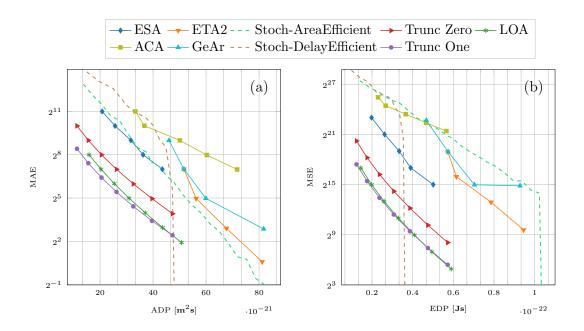

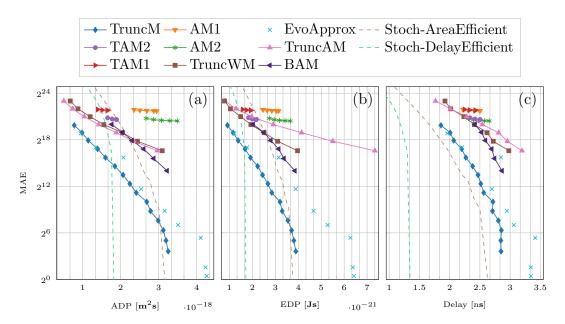

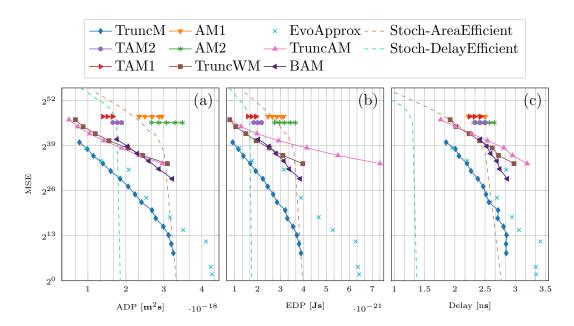

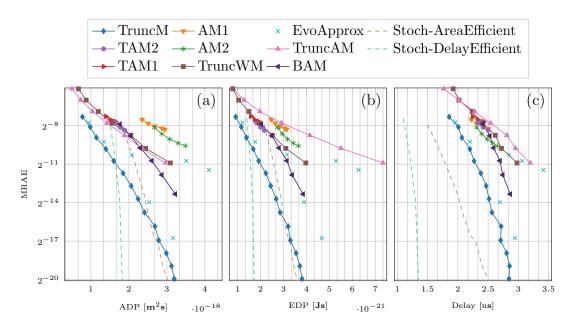

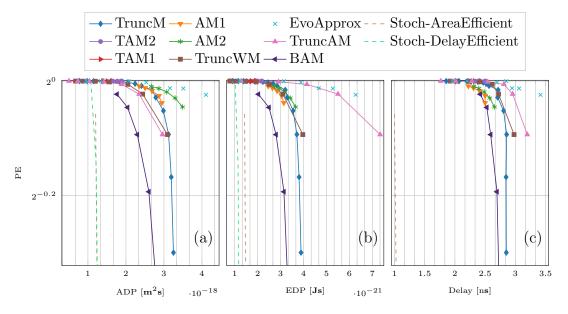

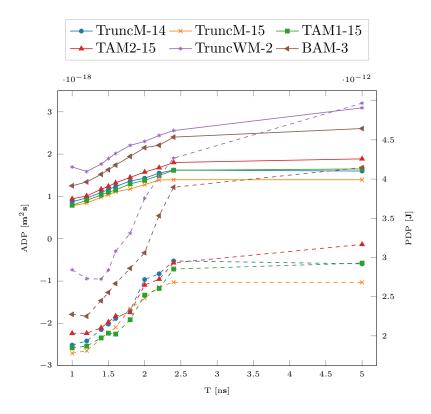

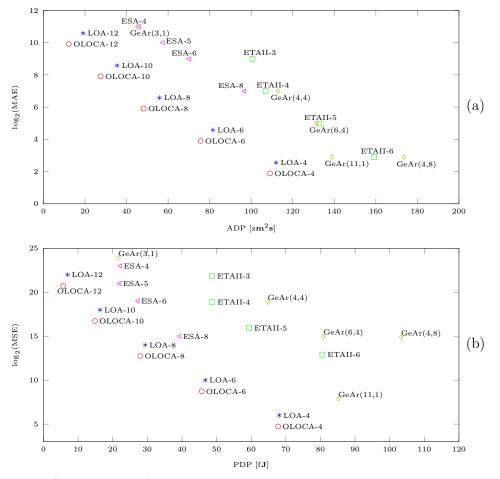

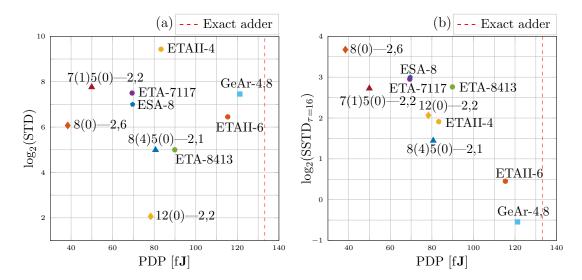

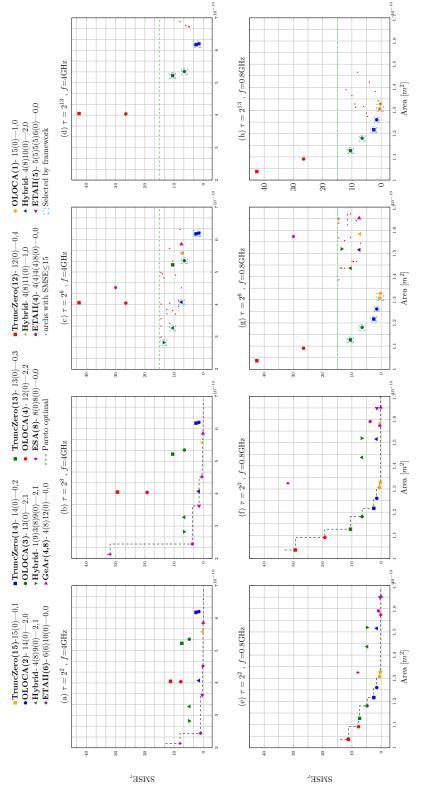

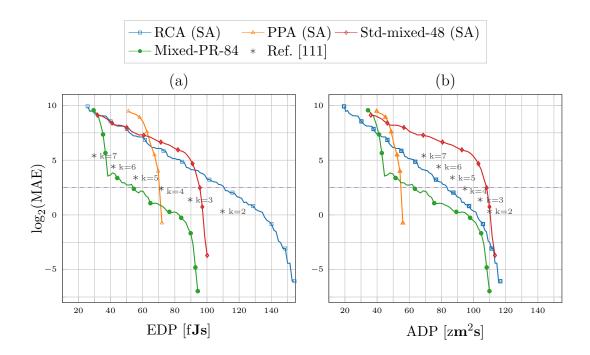

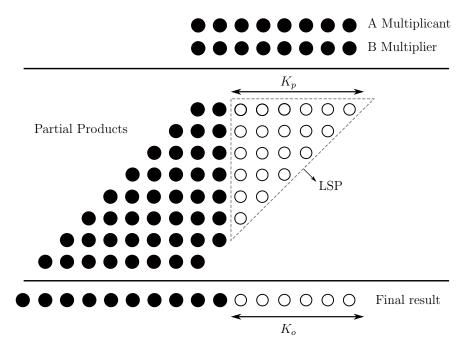

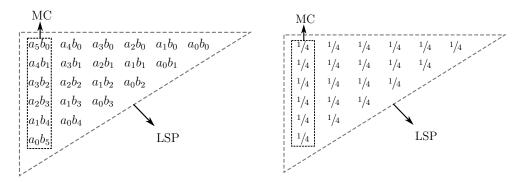

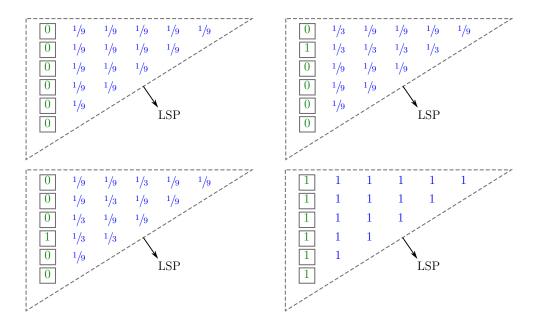

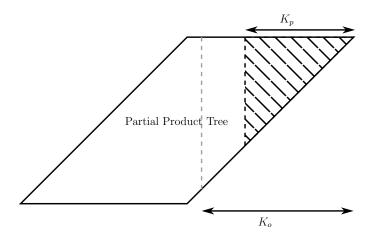

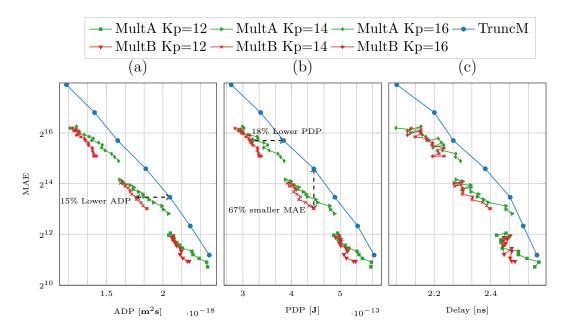

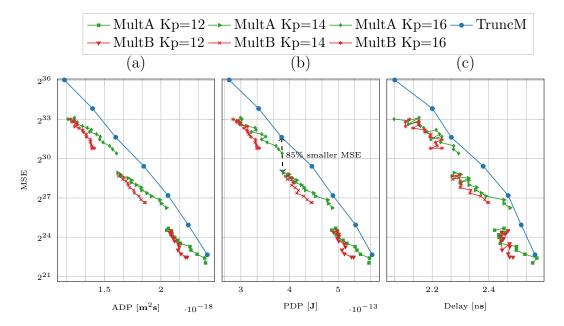

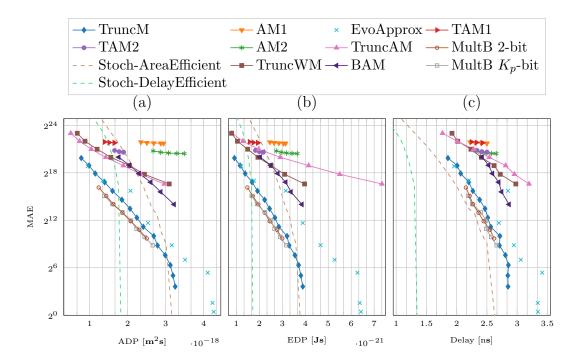

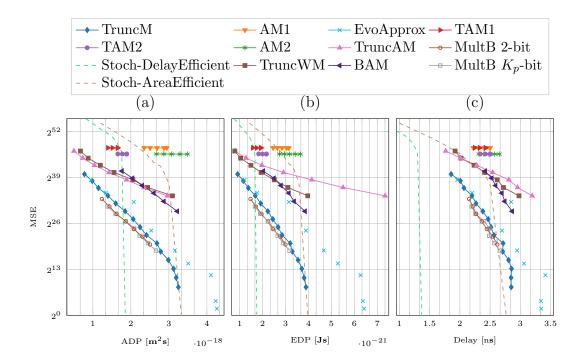

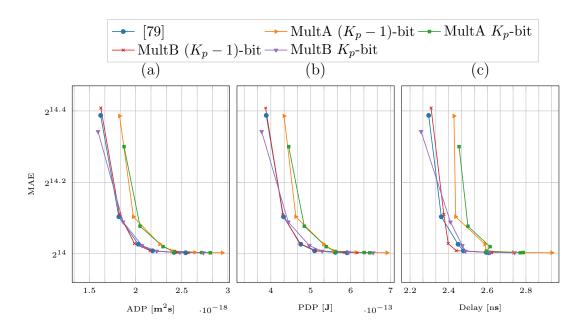

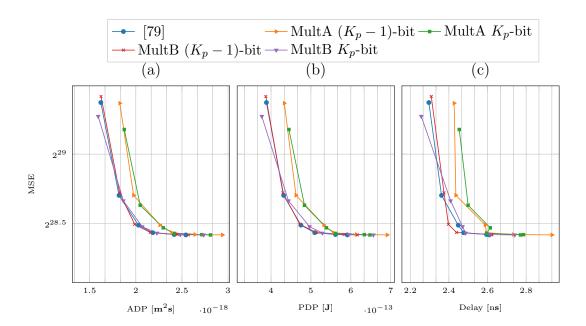

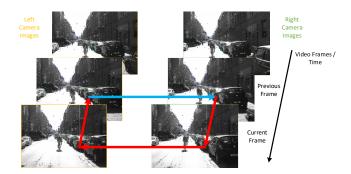

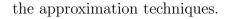

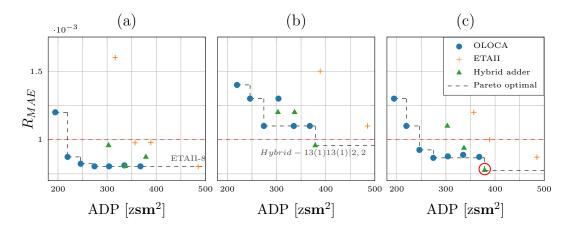

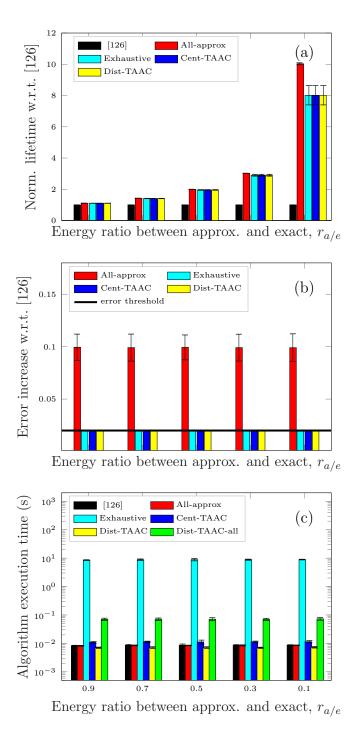

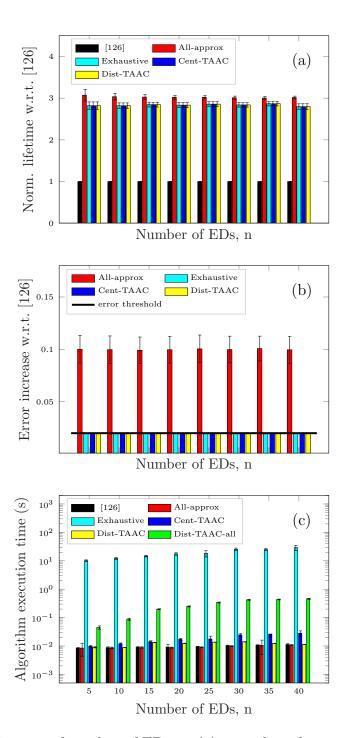

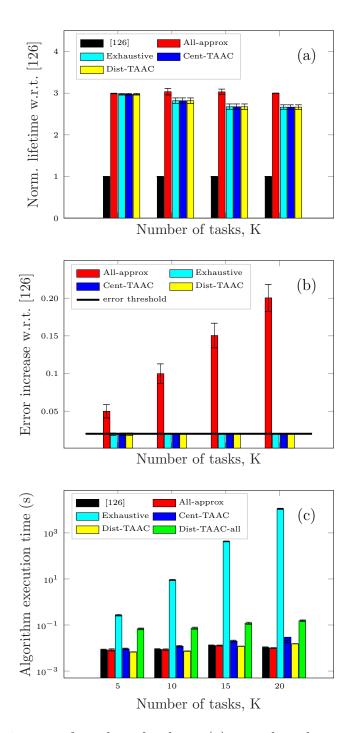

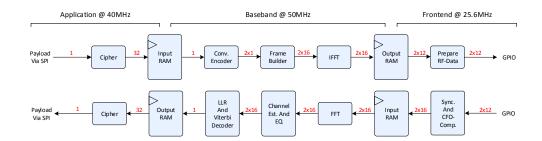

Fig. 3.1: Error histograms of a low-resolution input, a high-resolution input and an ANT output.