#### ANDRÉ REIN

## DRIVE

Dynamic Runtime Integrity Verification and Evaluation

### DRIVE

#### Dynamic Runtime Integrity Verification and Evaluation

Dissertation

zur Erlangung des akademischen Grades eines

Doktors der Ingenieurwissenschaften

– Dr.-Ing. –

vorgelegt von André Rein

im Fachbereich 03 (Mathematik/Informatik) der Universität Bremen

November 2018 – Version 1.0

Datum des Kolloquiums: 20.11.2018

1. Gutachter: Prof. Dr.-Ing. Carsten Bormann (Universität Bremen, Bremen)

2. Gutachter: Associate Prof. Dr. Carsten Rudolph (Monash University, Melbourne)

# Acknowledgements

In the years in which the results of this work have been completed, I have enjoyed the help of many amazing and extraordinary people. Without you, this work would never have been completed in this way, and I would like to express my sincere thanks to all of you.

First of all, I thank my advisor and supervisor, Professor Dr.-Ing. Carsten Bormann, for welcoming me and giving me the confidence to complete this thesis. It was a pleasure to work under your guidance, and I hope that in the future I will have the opportunity to work with you again. Next, I thank my second supervisor, Associate Professor Dr. Carsten Rudolph. We have known each other for several years now, and working under your guidance has always been a great honor and pleasure for me. Thank you very much for always believing in me; without you I would never have considered and completed a doctoral thesis. My heartfelt thanks also to Professor Dr. Nicolai Kunzte for driving me to start and finish this thesis. You have brought me to the exciting topic of security, and without your constant and untiring encouragement, help and guidance, there would be no acknowledgment because there would have been no thesis.

Furthermore, I thank everyone who was involved in the technical work of this thesis. In particular Hagen Lauer, you were a big help to me in the beginning and influenced this work decisively. In addition, many were involved in the implementation of the prototype. My special thanks to Wang Zhen, Professor Dr. Kai Oliver Detken, Marcel Jahnke, Thomas Rix, Malte Humann and Bernd Ritter for all your hard work and technical help. Without you, there would not have been such a professional prototype. Many thanks to all my current and former colleagues – Michael Eckel, Stefan Seefeldt and Mihai Serb – for all the technical discussions, advice and feedback.

My special thanks also go to all proofreaders. To Heike Stürmer, I am deeply grateful for the countless hours you have put into all the linguistic corrections. I am also especially grateful to Dr. Roland Rieke – your help and advice especially in the structuring and argumentation of this work were very helpful. Many thanks to Professor Dr. Igor Faynberg – you helped me a lot with the linguistic fine-tuning of this thesis. I would also like to express my special thanks to my former professors and especially to Professor Dr. Michael Jäger for all the enthusiasm that you have awakened in me and for working with you.

Many thanks to Huawei Technologies Germany and especially the Cyber Security and Privacy Lab team for this exciting topic and all your support during the last three years.

I thank my family and friends for all your support and for always believing in me. I thank my brother, Tommy, in particular for all the relaxing gaming sessions after many long days of writing.

Undoubtedly my deepest and most loving thanks belongs to my wife Denise. Although you would never admit it, I know you were suffering the most from the lack of time that I was unable to spend with you during the final months of completing this work. My deepest gratitude for all your love, your help and for being always there for me.

### **Abstract**

Cyberattacks have been rapidly and continuously gaining ground over the last few years, and there is an escalating conflict between those who develop new security techniques and those who develop new attacks that circumvent these countermeasures. This means that all security measures can and will ultimately be bypassed. In this context, attackers make use of advanced attack techniques that exploit the complexity of systems by first leveraging existing countermeasures and then using simpler attack techniques to take over the attacked system.

Classic security techniques add additional layers of safeguards by introducing patterns, compiler features like canary values or tainting, or hardware features for protecting systems against runtime attacks.

A different approach as presented in this thesis is the assessment of software that is based on a comparison of the binary code loaded and the memory image found during runtime. This approach rests on information data structures that are present in systems under attack. Parts of the loaded and executed memory image and its characteristics are predictable; therefore, by taking advantage of this predictability, a reliable assessment can be performed on the basis of various available pieces of information such as loaded binary files, loading mechanisms and allocated memory addresses. By using this information, it is possible to assess the memory state during execution by defining whitelists and policies based on the software actually used. This provides a new way to detect sophisticated runtime attacks on software that are not considered and recognized in current approaches. The evaluation of runtime system states is capable of making a significant contribution to system security.

Based on the evaluation of runtime states a novel and holistic runtime protection technology is presented which performs an assessment of runtime states of systems. In particular, this thesis sets forth the background, design, implementation and evaluation of a memory protection concept at runtime. This concept is based on an assessment of memory contents and meta information that are verified using trusted binary sources and policies.

The results of this work demonstrate that the developed runtime protection technology is a suitable solution and an appropriate addition to further increase the overall security of systems used today. A careful analysis and evaluation of the presented concept on the basis of a prototypical implementation prove the effectiveness of this technology.

The work presented builds the foundation for further research in the field, since the developed concept is widely adoptable in many modern systems. Specifically, with regard to virtualized environments, mobile systems or the Internet of Things, further research is necessary because the presented details must be adapted to match these other use cases or utilize different technologies/building blocks that are specific to the particular scenarios.

# Zusammenfassung

Cyberangriffe haben in den letzten Jahren rasch und kontinuierlich zugenommen. Hierbei herrscht ein Wettrennen zwischen der Entwicklung neuer Sicherheitstechniken und neuen Angriffen, die diese Gegenmaßnahmen umgehen. Diese Entwicklung bedeutet, dass letztendlich alle Sicherheitsmaßnahmen umgangen werden können und werden. Angreifer nutzen hierzu fortgeschrittene Angriffstechniken, die die Komplexität von Systemen ausnutzen, indem sie zunächst vorhandene Gegenmaßnahmen aushebeln und dann einfachere Angriffstechniken einsetzen, um das angegriffene System zu übernehmen.

Klassische Sicherheitstechniken fügen den Systemen zusätzliche Schutzebenen hinzu, indem sie Muster, Compilererweiterungen – z.B. Canaries oder Tainting – oder Hardwareerweiterungen zum Schutz von Systemen vor Laufzeitangriffen einführen.

Ein alternativer Ansatz, wie er in dieser Arbeit vorgestellt wird, ist die Bewertung von Software, die auf einem Vergleich zwischen dem geladenen Binärcode und dem während der Laufzeit gefundenen Speicherbild basiert. Dieser Ansatz beruht auf Datenstrukturen und Informationen, die in angegriffenen Systemen vorhanden sind. Dabei sind Teile des geladenen und ausgeführten Speicherabbildes und dessen Eigenschaften vorhersagbar. Dies bedeutet, dass unter Ausnutzung dieser Vorhersagbarkeit eine zuverlässige Bewertung auf der Basis verschiedener verfügbarer Informationen wie geladener Binärdateien, Lademechanismen und zugeordnete Speicheradressen durchgeführt werden kann. Durch die Verwendung dieser Informationen ist es möglich, den Speicherzustand während der Ausführung zu bewerten, indem sog. Whitelists und Richtlinien definiert werden, die auf der tatsächlich verwendeten Software selbst basieren. Dies bietet eine neuartige Möglichkeit komplexe Laufzeitangriffe auf Software zu erkennen, die in aktuellen Ansätzen nicht berücksichtigt wird und daher nicht erkennbar ist. Demnach leistet eine Auswertung von Laufzeitsystemzuständen einen wesentlichen Beitrag zur Systemsicherheit.

Basierend auf der Auswertung von Laufzeitzuständen wird eine neuartige und ganzheitliche Laufzeitschutztechnologie vorgestellt, die eine Bewertung der Laufzeitzustände von Systemen durchführt. Insbesondere wird in dieser Arbeit der Hintergrund, das Design, die Implementierung und die Evaluierung eines Speicherschutzkonzeptes zur Laufzeit vorgestellt. Dieses Konzept basiert auf der Bewertung von Speicherinhalten und Metainformationen, die unter zu Hilfenahme von vertrauenswürdigen binären Quellen und Richtlinien verifiziert werden.

Die Ergebnisse dieser Arbeit zeigen, dass die entwickelte Laufzeitschutztechnologie eine geeignete Lösung und sinnvolle Ergänzung ist, um die Gesamtsicherheit von heute eingesetzten Systemen weiter zu erhöhen. Eine sorgfältige Analyse und Bewertung des vorgestellten Konzepts, anhand einer prototypischen Umsetzung, belegt hierzu die Wirksamkeit dieser Technologie.

Da das entwickelte Konzept in vielen modernen Systemen weithin anwendbar ist, bildet die hier vorgestellte Arbeit eine Basis für die weitere Forschung auf diesem Gebiet. Insbesondere in Themengebieten wie virtualisierten Umgebungen, mobilen Systemen oder dem Internet der Dinge sind weitere Recherchen notwendig. Hierzu müssen die vorgestellten Details speziell auf den jeweiligen Anwendungsfälle angepasst werden, da unterschiedliche Technologien oder Bausteine zum Einsatz kommen und somit spezifische Implementierung benötigt werden.

### List of Publications

- [1] Andre Rein. "DRIVE: Dynamic Runtime Integrity Verification and Evaluation". In: *Proceedings of the 2017 ACM on Asia Conference on Computer and Communications Security ASIA CCS '17.* ACM Press, 2017, pp. 728–742. ISBN: 978-1-4503-4944-4. URL: http://dl.acm.org/citation.cfm?doid=3052973.3052975

- [2] Kai-Oliver Detken, Marcel Jahnke, Thomas Rix, and Andre Rein. "Software-design for internal security checks with dynamic Integrity Measurement (DIM)". in: 2017 9th IEEE International Conference on Intelligent Data Acquisition and Advanced Computing Systems: Technology and Applications (IDAACS). vol. 1. IEEE, Sept. 2017, pp. 367–373. DOI: 10.1109/idaacs.2017.8095106

- [3] Andre Rein, Roland Rieke, Michael Jaeger, Luigi Coppolino, and Nicolai Kuntze. "Trust Establishment in Cooperating Cyber-Physical Systems". In: *Cybersecurity of Industrial Control Systems, Security of Cyber Physical Systems*. Springer International Publishing, 2016, pp. 31–47. DOI: 10.1007/978-3-319-40385-4\_3

# Contents

| 1 | Intro | oduction                                               |

|---|-------|--------------------------------------------------------|

|   | 1.1   | Motivation                                             |

|   | 1.2   | Problem Description and Research Topic                 |

|   | 1.3   | Use Case                                               |

|   | 1.4   | Research Questions, Goals and Objectives               |

|   |       | 1.4.1 Research Questions                               |

|   |       | 1.4.2 Research Goal                                    |

|   |       | 1.4.3 Research Objectives                              |

|   | 1.5   | Research Plan and Methods                              |

|   | 1.6   | Contributions                                          |

|   | 1.7   | Outline                                                |

| 2 | Tech  | nnical Background 13                                   |

|   | 2.1   | Program Execution Principles in Computer Architectures |

|   | 2.2   | Program Loading in Modern Operating Systems            |

|   |       | 2.2.1 Organization of Program Text and Data            |

|   |       | 2.2.2 Loading Processes of Programs                    |

|   | 2.3   | Program Text Variants                                  |

|   |       | 2.3.1 Relocatable Code                                 |

|   |       | 2.3.2 Position Independent Code                        |

|   |       | 2.3.3 Program Text Distribution Analysis               |

|   |       | 2.3.4 Global Offset Table                              |

|   | 2.4   | Memory Management, Access and Protection               |

|   |       | 2.4.1 Virtual Memory Management                        |

|   |       | 2.4.2 File to Memory Mapping                           |

|   |       | 2.4.3 Access Rights of Memory Mapped Segments          |

|   |       | 2.4.4 Static and Dynamic Behavior of Programs          |

|   | 2.5   | Summary                                                |

| 3 | Secu  | urity Analysis 25                                      |

|   | 3.1   | Malware                                                |

|   |       | 3.1.1 Malware Types                                    |

|   |     | 3.1.2   | Malware Key Properties                                 | 27  |

|---|-----|---------|--------------------------------------------------------|-----|

|   |     | 3.1.3   | Summary                                                | 33  |

|   | 3.2 | System  | n Memory Runtime Attacks                               | 34  |

|   |     | 3.2.1   | Attack Overview                                        | 34  |

|   |     | 3.2.2   | Control Flow Attack Foundation                         | 36  |

|   |     | 3.2.3   | Types of Control Flow Manipulation and Bending Attacks | 38  |

|   |     | 3.2.4   | Countermeasures                                        | 50  |

|   |     | 3.2.5   | Summary                                                | 55  |

|   | 3.3 | Threat  | and Attack Model                                       | 56  |

|   |     | 3.3.1   | Attack Goals                                           | 56  |

|   |     | 3.3.2   | Attack Methods and Procedures                          | 58  |

|   |     | 3.3.3   | Multi-Step Hybrid Attacks                              | 58  |

|   |     | 3.3.4   | Attack Scenarios                                       | 65  |

|   |     | 3.3.5   | Limitations                                            | 70  |

|   |     | 3.3.6   | Summary                                                | 70  |

|   | 3.4 | Trust N | Model and Security Assumptions                         | 71  |

|   | 3.5 | Securit | ty Analysis Summary and Conclusion                     | 72  |

|   |     |         |                                                        |     |

| 4 |     | _       | h Level Attestation Concept and Architecture           | 75  |

|   | 4.1 |         | Level Attestation Concept                              | 76  |

|   | 4.2 |         | E High Level Architecture                              | 77  |

|   |     | 4.2.1   | Architecture Overview                                  | 78  |

|   |     | 4.2.2   | Instantiated Software Architecture                     | 80  |

|   |     | 4.2.3   | Summary                                                | 83  |

|   | 4.3 |         | ecture Deployment Analysis                             | 84  |

|   |     | 4.3.1   | Isolation during Verification                          | 84  |

|   |     | 4.3.2   | Isolation during Measurement and Reporting             | 88  |

|   |     | 4.3.3   | Design Space and Architectural Limitations             | 92  |

|   |     | 4.3.4   | Summary                                                | 94  |

|   | 4.4 | Conce   | pt and Architecture Summary and Conclusion             | 95  |

| 5 | DRI | VE Mea  | asurement, Verification and Reporting Concept          | 97  |

|   | 5.1 |         | ation of Static Information                            | 97  |

|   |     | 5.1.1   | Measurement of Static Memory Areas                     | 98  |

|   |     | 5.1.2   | Reporting of Measured Data                             | 102 |

|   |     | 5.1.3   | Remote Attestation Protocol                            | 104 |

|   |     | 5.1.4   | Verification of Reported Static Measurement Data       | 109 |

|   |     | 5.1.5   | Summary                                                | 111 |

|   | 5.2 |         | ation of Predictable Dynamic Information               | 112 |

|   |     | 5.2.1   | Measurement of Relocatable Code                        |     |

|   |     | 5.2.2   | Verification of Relocatable Code                       | 113 |

|   |     | 5.2.3   | Measurement of Global Offset Tables                    | 115 |

|   |     | 5.2.4   | Verification of Global Offset Tables                   | 116 |

|   |     | 5.2.5   | Summary                                                | 118 |

|   | 5.3 |         | ation of Unpredictable Dynamic Information             |     |

|     |              | 5.3.1   | Measurement of Unpredictable Dynamic Information       | 119 |  |  |

|-----|--------------|---------|--------------------------------------------------------|-----|--|--|

|     |              | 5.3.2   | Verification of Unpredictable Dynamic Segments         | 121 |  |  |

|     |              | 5.3.3   | Summary                                                | 124 |  |  |

|     | 5.4          | Conce   | ot Security Analysis and Evaluation                    | 124 |  |  |

|     |              | 5.4.1   | Static Information Attestation Analysis                | 125 |  |  |

|     |              | 5.4.2   | Predictable Dynamic Information Attestation Analysis   | 127 |  |  |

|     |              | 5.4.3   | Unpredictable Dynamic Information Attestation Analysis | 129 |  |  |

|     |              | 5.4.4   | Summary                                                | 131 |  |  |

|     | 5.5          | Chapte  | er Summary                                             | 132 |  |  |

| 6   | Impl         | ementa  | tion and Evaluation                                    | 133 |  |  |

|     | 6.1          | DRIVE   | Proof of Concept Implementation                        | 133 |  |  |

|     |              | 6.1.1   | DRIVE Software Architecture Implementation             | 134 |  |  |

|     |              | 6.1.2   | DRIVE Component Guideline Implementation               | 139 |  |  |

|     |              | 6.1.3   | Summary                                                | 144 |  |  |

|     | 6.2          | Securit | ry Evaluation                                          | 144 |  |  |

|     |              | 6.2.1   | Attack-based Security Analysis                         | 145 |  |  |

|     |              | 6.2.2   | Summary and Conclusion                                 | 149 |  |  |

|     | 6.3          | Perform | mance and Scalability Evaluation                       | 150 |  |  |

|     |              | 6.3.1   | Evaluation Summary Original Research                   | 151 |  |  |

|     |              | 6.3.2   | Proof of Concept Measurement Evaluation                | 152 |  |  |

|     |              | 6.3.3   | Summary                                                | 157 |  |  |

|     | 6.4          | Implen  | mentation and Evaluation Summary                       | 158 |  |  |

| 7   | State        | of the  | Art and Related Work                                   | 161 |  |  |

|     | 7.1          | File-ba | sed Integrity Protection during Load Time              | 162 |  |  |

|     |              | 7.1.1   | Measured Boot                                          | 162 |  |  |

|     |              | 7.1.2   | Secure Boot                                            | 163 |  |  |

|     | 7.2          | Integri | ty Protection during Runtime of Programs               | 164 |  |  |

|     |              | 7.2.1   | Integrity Protection of Static Memory Content          | 164 |  |  |

|     | 7.3          | Contro  | ol Flow and Data Flow Integrity                        |     |  |  |

|     |              | 7.3.1   | Control Flow Integrity                                 | 168 |  |  |

|     |              | 7.3.2   | Data Flow Integrity                                    | 169 |  |  |

| 8   | Cond         | clusion | and Outlook                                            | 171 |  |  |

|     | 8.1          | Conclu  | asion                                                  | 171 |  |  |

|     |              | 8.1.1   | Contributions                                          | 171 |  |  |

|     |              | 8.1.2   | Research Questions and Objectives                      | 173 |  |  |

|     | 8.2          | Outloo  | ok and Future Work                                     | 179 |  |  |

| Bil | bliogr       | aphy    |                                                        | 183 |  |  |

| Ac  | ronyn        | ns      |                                                        | 195 |  |  |

| No  | otations 198 |         |                                                        |     |  |  |

# List of Figures

| 2 To | echnical Background                                                  |    |

|------|----------------------------------------------------------------------|----|

| 2.1  | ELF to VAS Mapping                                                   | 15 |

| 2.2  | ELF File Representation                                              | 21 |

| 3 S  | ecurity Analysis                                                     |    |

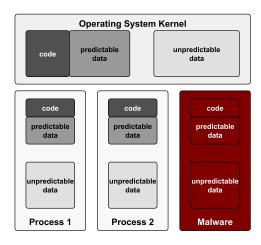

| 3.1  | Type-0 Malware Stealthiness Classification                           | 29 |

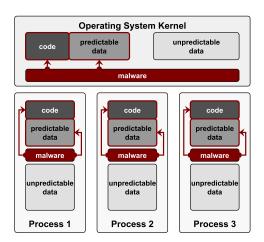

| 3.2  | Type-1 Malware Stealthiness Classification                           | 29 |

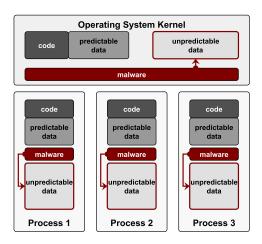

| 3.3  | Type-2 Malware Stealthiness Classification                           | 30 |

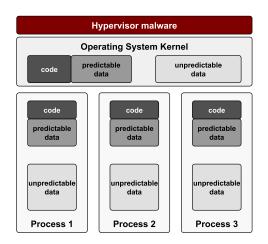

| 3.4  | Type-3 Malware Stealthiness Classification                           | 30 |

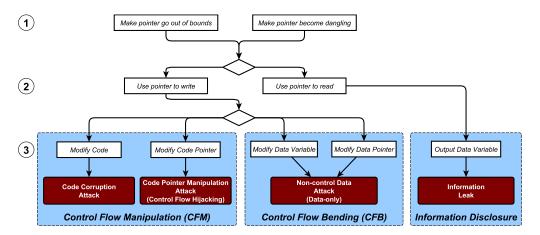

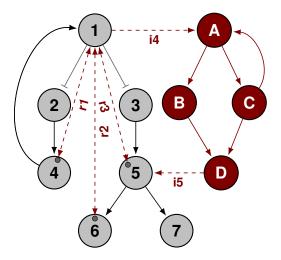

| 3.5  | Exploitation Model and Classification of Attacks                     | 35 |

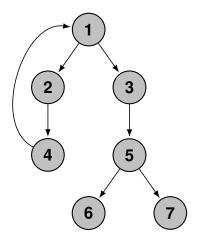

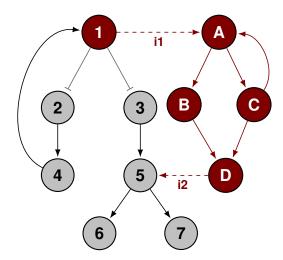

| 3.6  | CFG with multiple valid Nodes and Branches                           | 37 |

| 3.7  | CFG with injected Malicious Code and Modified Branch                 | 39 |

| 3.8  | CFG with maliciously modified Code                                   | 40 |

| 3.9  | CFG with maliciously modified Code Pointer                           | 43 |

| 3.10 | CFG with maliciously modified Code pointer to Shared Library         | 43 |

| 3.11 | ROP: CFG calling Instruction Sequences (Gadgets) inside Nodes        | 45 |

| 3.12 | CFG including malicious Data Modifications                           | 46 |

| 3.13 | Hybrid CFM combining a Code Reuse, Code Injection and CPM attack     | 48 |

| 3.14 | Long Term Goals and Attack Methods                                   | 57 |

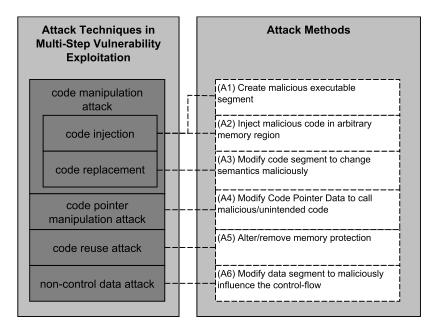

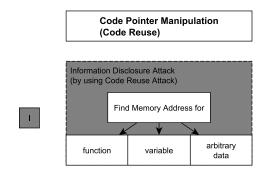

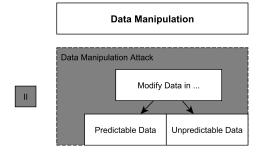

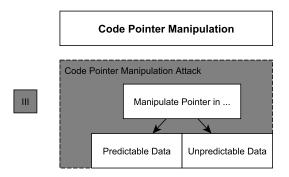

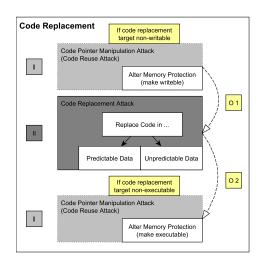

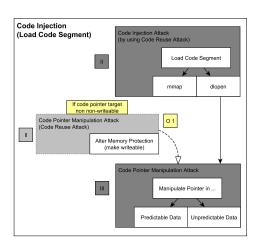

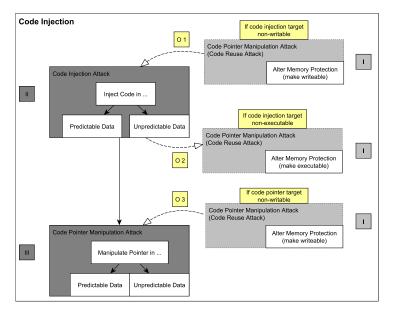

| 3.15 | Vulnerability Exploitation Techniques and Methods                    | 59 |

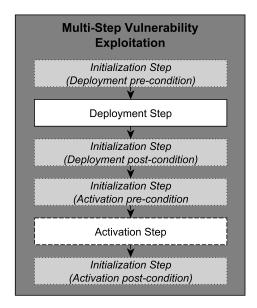

| 3.16 | Different Steps in Multi-Step Vulnerability Exploitation             | 60 |

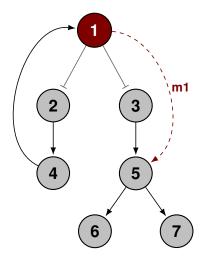

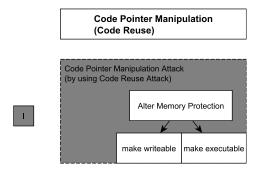

| 3.17 | CPMAP 1: typical Step 1 Attack                                       | 61 |

| 3.18 | IDAP 1: typical Step 1 Attack                                        | 61 |

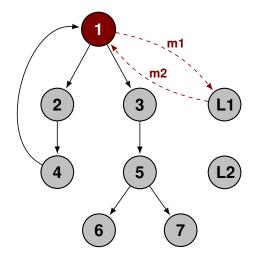

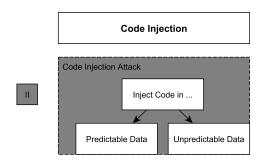

| 3.19 | CIAP 1: typical Step 2 Code Injection Attack                         | 62 |

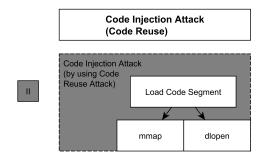

| 3.20 | CIAP 2: typical Step 2 Code Injection Attack                         | 62 |

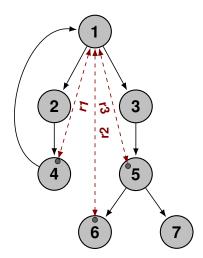

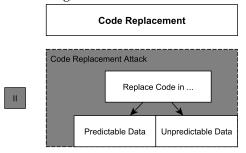

| 3.21 | RCAP 1: typical Step 2 Code Replacement Attack                       | 62 |

| 3.22 | DMAP 1: typical Step 2 Data Manipulation Attack                      | 62 |

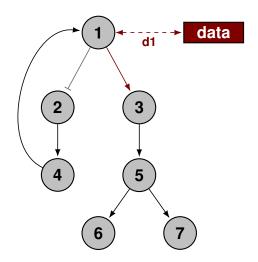

| 3.23 | CPMAP 2: typical Step 3 Code Pointer Manipulation Attack             | 63 |

| 3.24 | Code Replacement Attack with optional Memory Permission Modification | 64 |

| 3.25 | Code Injection Attack with optional Memory Permission Modification | 64  |

|------|--------------------------------------------------------------------|-----|

|      | Complex Code Injection Attack                                      | 64  |

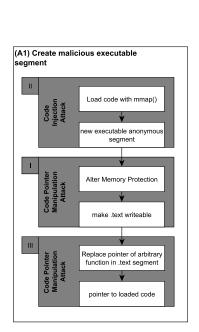

| 3.27 | A1: Create Malicious Executable Segment                            | 65  |

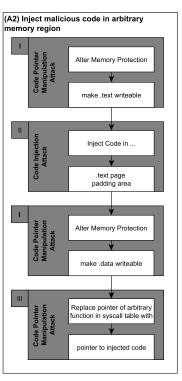

| 3.28 | A2: Inject Malicious Code in arbitrary Memory Region               | 65  |

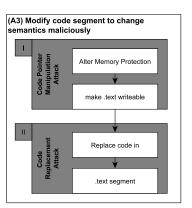

| 3.29 | A3: Modify Code Segment to change Semantics maliciously.           | 65  |

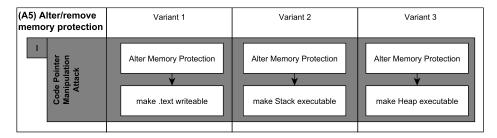

| 3.30 | A5: Alter/Remove Memory Protection                                 | 68  |

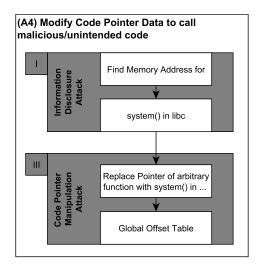

| 3.31 | A4: Modify Code Pointer Data to call Malicious/Unintended Code     | 68  |

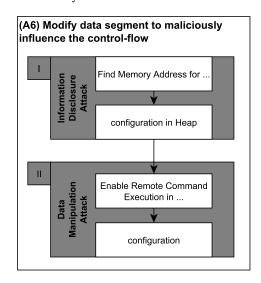

| 3.32 | A6: Modify Data Segment to maliciously alter the Control Flow      | 68  |

| 4 C  | ORIVE High Level Attestation Concept and Architecture              |     |

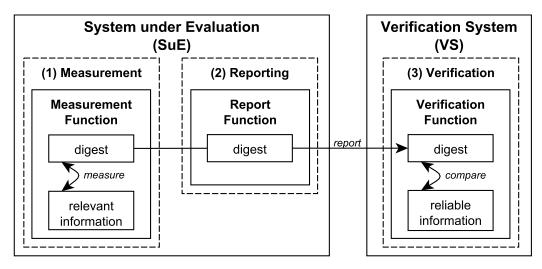

| 4.1  | High Level Attestation Concept based on Digests                    | 76  |

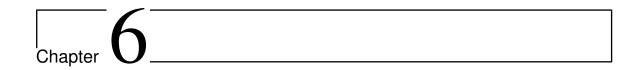

| 4.2  | DRIVE Architecture for Measurement, Reporting and Verification     | 78  |

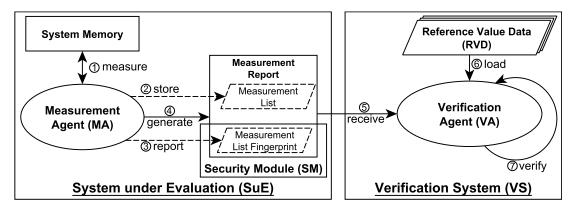

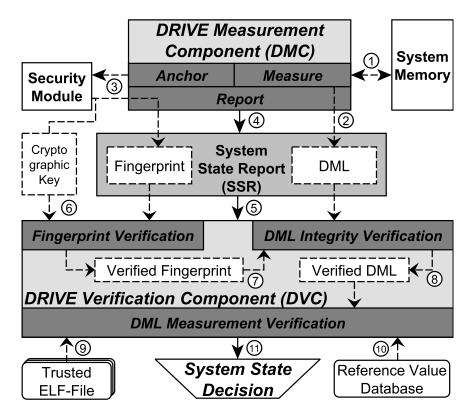

| 4.3  | DRIVE Measurement, Reporting and Verification Process Overview     | 81  |

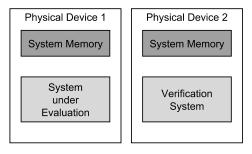

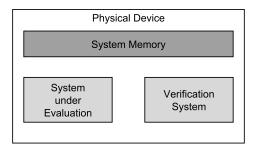

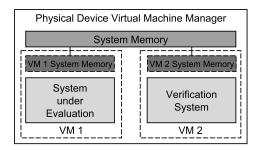

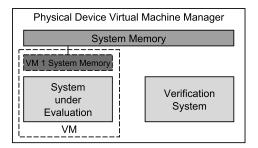

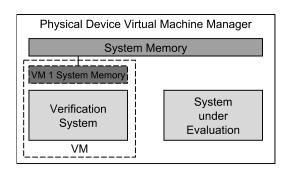

| 4.4  | Deployment of SuE and VS Example 1                                 | 85  |

| 4.5  | Deployment of SuE and VS Example 2                                 | 85  |

| 4.6  | Isolated Deployment of SuE and VS Example 1                        | 86  |

| 4.7  | Isolated Deployment of SuE and VS Example 2                        | 86  |

| 4.8  | Inconclusive virtualized Deployment of SuE and VS                  | 86  |

| 5 D  | ORIVE Measurement, Verification and Reporting Concept              |     |

| 5.1  | Measurement Set Composition                                        | 101 |

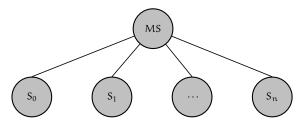

| 5.2  | Remote Attestation Protocol for DRIVE                              | 105 |

| 5.3  | Relevant Program Header Information from /bin/bash                 | 110 |

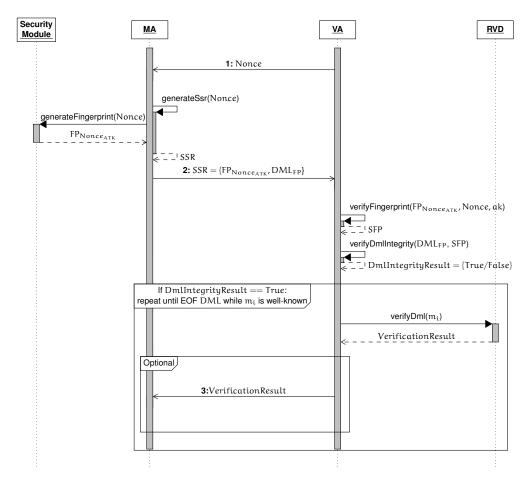

| 5.4  | Verification Excerpt of the GOT Layout and Symbol Resolution       | 117 |

| 6 I1 | mplementation and Evaluation                                       |     |

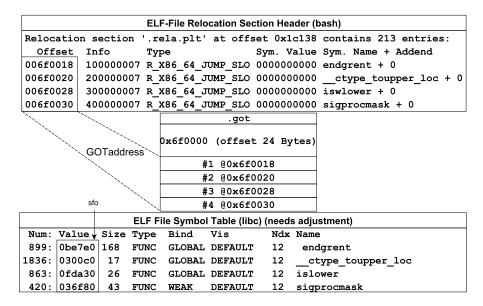

| 6.1  | Software Components Architecture                                   | 134 |

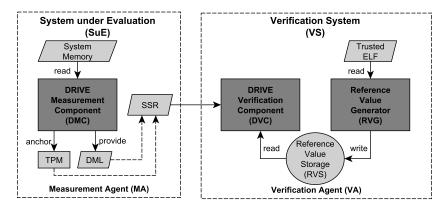

| 6.2  | DRIVE Measurement Component Subcomponents                          | 135 |

| 6.3  | Excerpt of an SSR for /bin/bash                                    | 137 |

# List of Tables

| 2 T                                           | Fechnical Background                                                                                                                                                                                                                                                                                                                                     |                                        |

|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 2.1<br>2.2<br>2.3                             | Program Text Variant Analysis for Shared Libraries                                                                                                                                                                                                                                                                                                       | 19<br>19<br>22                         |

| 3 S                                           | Security Analysis                                                                                                                                                                                                                                                                                                                                        |                                        |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7 | Stealthiness Classification of Malware.  Persistence Classification of Malware.  Stealthiness and Persistence Properties of Code Corruption Attacks  Properties of Code Pointer Manipulations  Stealthiness and Persistence Properties of Non-control Data Attacks  Hybrid Attack Stealthiness and Persistence  Memory Manipulations conducted by Attack | 31<br>32<br>42<br>44<br>47<br>49<br>69 |

| 4 E                                           | ORIVE High Level Attestation Concept and Architecture                                                                                                                                                                                                                                                                                                    |                                        |

| 4.1<br>4.2<br>4.3<br>4.4                      | Isolation Grades for different SuE and VS Deployments                                                                                                                                                                                                                                                                                                    | 87<br>88<br>91<br>91                   |

| 5 E                                           | ORIVE Measurement, Verification and Reporting Concept                                                                                                                                                                                                                                                                                                    |                                        |

| 5.1<br>5.2<br>5.3<br>5.4                      | Hashed Measurement Sets HMS                                                                                                                                                                                                                                                                                                                              | 108                                    |

### 6 Implementation and Evaluation

| 6.1 | Access Permission Manipulation Detection during Attestation         | 145 |

|-----|---------------------------------------------------------------------|-----|

| 6.2 | Manipulation Detection of predictable and unpredictable Information | 147 |

| 6.3 | Performance Metrics for Measurement Component                       | 153 |

| 6.4 | Evaluation Benchmark Experiment 1                                   | 154 |

| 6.5 | Evaluation Benchmark Experiment 2                                   | 155 |

| 6.6 | Evaluation Benchmark Experiment 3                                   | 156 |

# List of Listings

### 5 DRIVE Measurement, Verification and Reporting Concept

| 5.1 | Bash ELF Program Header Excerpt                           | 99  |

|-----|-----------------------------------------------------------|-----|

| 5.2 | Using dd to extract the text Segment from Bashs' ELF file | 110 |

| 5.3 | Generating a sha256sum of an extracted Bash text Segment  | 110 |

| 5.4 | Program Headers from Bash ELF                             | 121 |

| 5.5 | Section to Segment Mapping Information from Bash ELF      | 122 |

### Introduction

#### 1.1 Motivation

The complexity and number of cyberattacks have been rapidly increasing over the last few years. Specifically, during the last eight years, very complex attacks were detected that targeted a broad range of industries and governmental institutions – e.g. Iran nuclear facilities StuxNet (2010) [4], Belgacom & Bengal Mobile (2013) [5], J.P. Morgan (2014) [6], German Bundestag (2015) [7], Ruag AG (2016) [8]. These sophisticated attacks are known as Advanced Persistent Threats (APTs) and pose a substantial threat to many infrastructures due to their high complexity, evasiveness and diversity, rendering effective detection exceptionally difficult. Moreover, APTs are particularly tailored to circumvent broadly adopted and widely used countermeasures, for instance, firewalls, virus scanners and intrusion detection systems. As a consequence, APTs are usually detected a long time after their initial deployment and detection is often coincidental, e.g. based on suspicious findings during network traffic analysis.

However, the behavior of a computer system or, a device acting as a part of an IT-infrastructure, is defined by the software running on the system. Thus, nearly every attack exploiting a software vulnerability interacts with the system's memory to a certain extent. Often, systems are attacked by simply replacing or adding malicious software components permanently and executing them as desired. Those illicit modifications may occur both off-line, for instance, by malicious firmware manipulation, and during system runtime, usually by exploitation of well-known vulnerabilities like buffer overflows, format string, and write-what-where vulnerabilities, c.f. [9, 10]. Yet, the detection of persistent modifications on the file system level is well researched, and anti-virus/malware tools have been available for more than 30 years. Moreover, the measurement and attestation of system states, based on integrity verification of loaded software, is also well understood.

Still, the objective is not always permanent system file modification; instead, system infiltration often utilizes runtime memory and control-flow manipulation in order to

launch a successful attack. This means that the actual manipulation is conducted only in volatile memory and leaves no evidence inside permanent storage areas on the targeted system. Particularly in these cases, integrity measurement and anti-virus tools do not provide protection, because both rely on files and do not consider memory content. For instance, anti-virus tools were found to be ineffective in terms of file-less malware, c.f. [11]. Yet even those non-permanent attacks leave trails and can be detected inside the volatile system memory. Memory forensics [12] enables the detection of maliciously tampered volatile memory. Memory forensics tools and techniques, capable of detecting even the most sophisticated attacks, can be used to analyze suspicious system behavior. However, the field of memory forensics is not thoroughly researched and well understood [13]. Nonetheless, certain memory forensics tools exist, c.f. [14–16] that are able to extract system memory content during runtime and facilitate further system analysis. But these tools are only usable with expert knowledge in both memory forensics and attack vectors and, moreover, require an initial detection of any suspicious behavior.

Because current security technologies do not provide the capability for automated runtime state assessments, this thesis enhances the classic onetime software component attestation approaches from load-time toward continuous monitoring and attestation throughout the entire software component's lifetime. This enhancement facilitates the successful detection of complex malicious threats and thus helps to significantly reduce adversaries' capabilities and the time span of successful and long-lasting attacks.

#### 1.2 Problem Description and Research Topic

In order for operators to ensure that a system or service still fulfills its primary objective, it is necessary to determine whether the system behaves as intended. Once a system transforms into an unknown or indecisive state, its functionality becomes completely unpredictable. In some cases, this transition could simply imply that a wrong or unknown configuration was intentionally deployed to the system. But in other more severe cases, it could also indicate that the system was unintentionally tampered with by a malicious adversary, causing the system to be fully or partially compromised.

In either case, an operator requires reliable information about the system state in order to perform necessary actions. For instance, the operator could simply report the system state or do nothing if no modification was detected; deploy a known configuration or software in benign cases; observe or analyze the system more closely; or instantly isolate or disable the system in severe cases and security-sensitive environments.

The acquisition of this reliable information is currently limited to state information only covering a fraction of the system state at a single point in time, i.e. the load-time of a software component. Although this load-time information is vital for a system state classification, the vast majority, i.e. the runtime state of the software component, is not

covered by current approaches and thus not considered for any classification process.

Accordingly, the research in this work will focus on the topic of continuous acquisition and classification of reliable system state information, also known as system attestation, based on state information acquired during software components' runtime. This runtime information provides the most recent details of software components' states and can be considered as one of the last characteristics that can be effectively observed on a system without interfering with the exact runtime behavior on the instructional level. This will enable a security classification of systems based on more relevant state information and thus the application of more definite actions, such as applying remediation strategies, based on the classification carried out.

#### 1.3 Use Case

An operator owns, manages and operates a set of devices that form an operational network. In order to be able to offer customers reliable services, it is necessary to obtain reliable information about the current status of a device. This state may include, for example, the overall state of this system, including all determinable components, or may be limited to certain relevant components required for the reliable provision of its service. It is therefore necessary to determine whether a device or considered subcomponents of its system are still in a benign state or have been compromised.

The state is mostly defined by the software that is executed on the system. Therefore, the operator needs to determine whether the software, in particular the Operating System (OS) and running applications, are still configured and executed as intended. For instance, the operator wants to know that only certain applications – in particular versions – are executed. In case an unintended application is executed, the device may be considered as malicious and should be handled accordingly, for example, being isolated from the operational network.

There are many possible solutions to the problems of detecting and preventing the execution of unintended programs. One solution would be a *Measured Boot* along with an *Attestation*, c.f. [17, 18], used to detect the execution of unintended software. In addition to that, *Secure Boot* [19] that applies code signing techniques [20] can be used to prevent the execution of software that lacks a valid signature. However, both solutions are not designed nor are they suitable to detect or prevent attacks that happen after the initial loading of the software.

Since the operator is interested in the current state of the device, the information about the initial loading of the software is not enough. This is because almost all software is susceptible to runtime attacks that can modify the intended purpose of the software during its execution and, hence, execute arbitrary malicious functions. As a result, the once-loaded software may have taken on a malicious state not detectable by the deployed

integrity protection mechanisms.

The most recent information about the actual state of the software is always maintained inside the system memory. This means the in-memory representation of the software is the most current state information available. For this reason, the operator wants to attest the software's in-memory state, which is defined as the runtime state throughout this thesis. The operator must monitor, i.e. measure and compare the current runtime state against defined directives, in order to determine whether the software is still in a well-known benign state. It is only with this information that the operator can determine the current state of a device within her operational network and act accordingly when a malicious state is identified.

This thesis focuses on individual systems with the currently dominant architecture and assumes that the devices in the operational network contain a tamper-resistant *security module*, for instance a Trusted Platform Module (TPM), able to store the current system state and facilitate its secure reporting. Once a system state is stored inside the security module, it is assumed to be securely anchored and immutable to any modification without detection. The use case considered in this thesis, further assumes that:

- (1) the operator maintains a central management system in a specific trusted management network and

- (2) this trusted management network is strictly isolated from the operational network.

Therefore, only the network operator has access to the management systems and any service the management systems provide. Moreover, no one but the operator has access to the trusted management network; thus, no direct access from the operational network to the trusted management network is possible. This means that no one but the network operator can observe, intercept or tamper with communication data transferred via the trusted network. As a result, the devices inside the management network are considered trustworthy and, thus, can be used to securely maintain information to conduct a secure attestation of the measured information on the devices.

### 1.4 Research Questions, Goals and Objectives

#### 1.4.1 Research Questions

In order to gain a deeper understanding of how and to what extent systems are affected by attacks that target compromising software at runtime, as well as to suggest solutions for further increasing the resilience of such systems against runtime attacks, the following research questions will be addressed in the course of this work:

- (Q1) What are the capabilities, limitations and characteristics of software runtime attacks?

- **(Q2)** What is necessary to establish a protection technology that implements continuous and reliable monitoring of the runtime state of systems?

- **(Q3)** What are the capabilities, procedures and constraints of a continuous runtime protection technology?

- **(Q4)** How can a runtime protection technology be realized and assessed on the basis of a designed runtime protection technology?

#### 1.4.2 Research Goal

The overarching goal of this work aims at enhancing overall security capabilities by providing a runtime protection technology that considers attacks on the runtime state of modern computer systems. The protection technology should be able to monitor continuously runtime states of systems and determine on a different system whether monitored systems are still in a benign or transformed into a malicious state. This evaluation of the system state is to be carried out in a reliable and secure fashion so that the determination of the system state is evidence-proven.

The envisioned protection technology aims to advance the state-of-the-art technology in the field through enhancing and adapting concepts from both: (1) classic system attestation concepts – to securely collect, report and verify system states of software components and (2) memory forensics – to continuously observe, capture and analyze software components' runtime states. This should enable the successful detection of aforementioned attacks and provide evidence of whether a software component was illicitly modified during its runtime or not.

Based on the presented research questions and the goal, different objectives will be addressed during the course of this thesis. These objectives are presented next.

#### 1.4.3 Research Objectives

(RO1) Carry out a security analysis of runtime-related attacks and threats.

In order to develop a meaningful runtime protection technology, it is important to first obtain an overview of the current threat and attack landscape. For this reason, the first goal is to investigate and analyze current threats and attacks that allow software to be compromised at runtime. Next, it is also necessary to investigate well-known countermeasures that can be used to defend against attacks. It is essential to understand to what extent the countermeasures provide effective protection or how they can be circumvented. Finally, different attack scenarios have to be developed which allow a later evaluation of the security concept. This is important to examining the security technology being developed

in terms of its effectiveness in ensuring that the defense strategies developed are effective.

Accordingly, this research objective (RO1) addresses the research question (Q1) and provides input for (Q2).

**(RO2)** Establish and develop a flexible runtime protection technology concept and architecture.

Based on the security analysis performed, a flexible concept and architecture must be developed that considers the results of the security analysis thoroughly. Furthermore, the concept and the architecture are to implement a reliable and verifiable security concept that allows a third system to make a decision regarding the current system status and which allows it to be carried out repeatedly. Here, it is expected that concepts from well-known attestation procedures in the field of trusted computing and mechanisms from memory forensics will have to be combined in order to implement a sensible security technology that meets the given requirements. The developed concept and the architecture provide the framework by describing its building blocks. Therefore, these building blocks must be mapped to concrete components and described and analyzed in more detail.

This research objective (RO2) addresses the research question (Q2) and establishes a basis for the next research objective (RO3) that is meant to develop and provide the technical solution of the runtime protection technology.

(RO3) Describe, develop and provide an implementable runtime protection technology.

The technical details of the runtime protection technology must be refined on the basis of the developed architecture components. To do this, the components and their concrete mechanisms must be thoroughly defined, described and analyzed. It is important to ensure that the individual components of the runtime protection technology work together to attest runtime system states reliably, conclusively and repeatedly on a trustworthy third system. The level of detail of the mechanisms and procedures must be sufficiently detailed to allow the implementation of the entire designed runtime protection technology. In particular, the collection of measurement data, secure storage and transmission of these measurement data and verification of the measurement data must be ensured. It is equally important to evaluate the developed technology with regard to its security at this conceptual level. It is expected that the results of this analysis will provide important input for implementation and thus provide a coherent and secure overall solution.

This research objective (RO3) addresses the research question (Q3) and develops

a coherent, secure and implementable runtime protection technology. It will provide the basis for the next research objective (RO4), which is aimed at implementing and evaluating the runtime protection technology in a prototype in order to develop and provide the technical solution of the runtime protection technology.

**(RO4)** Adopt, implement and evaluate the developed runtime protection technology.

On the basis of the developed concept and architecture from (RO2) and on the basis of the technical descriptions of the mechanisms and procedures from (RO3), a prototype implementation of the runtime security technology will be adapted, implemented and evaluated. First of all, a software architecture has to be developed that realizes a concrete implementation of the architecture and implements the described mechanisms of the runtime security technology. Subsequently, the actual prototypical implementation must be carried out with the result of providing an overall operational system that implements the developed core components of the technology.

On the basis of this prototype, a security analysis will then be performed to illustrate to what extent the entire system can recognize the defined attack scenarios from (RO1). In addition, the prototype is to be evaluated for possible performance problems, and, if necessary, different optimization strategies will be tested.

#### 1.5 Research Plan and Methods

The research in this thesis relies on a variety of related existing solutions and results. Regarding the threat and attack analysis, many results and concepts in both academia and non-academia have been published and are well understood. In order to provide a meaningful solution, potential and current exploitation techniques, attack vectors, threats and software vulnerabilities must be carefully identified and thoroughly studied. Similarly, protective measures on the OS, isolation techniques and other security solutions must be carefully examined. As a result, this initial research facilitates the design and development of a strong and appropriate attack and threat model, which in turn builds the foundation for the runtime protection technology to be developed.

Regarding the runtime protection technology, both system integrity technologies for static- and runtime-measurement and memory forensics tools and concepts are readily available. The loading and address resolution processes as well as memory management are well-known and integral parts of the OS core functionality. For these reasons, the initial research will start with a deep analysis of well-known static system integrity measurement and verification schemes and an examination of the address resolution and loading process

for kernel and user space software components. In addition, the relationship between Executable and Linkable Format (ELF) files of encapsulated program texts on Linux- and Unix-based OSs and the loaded runtime artifacts will be analyzed with regard to user and kernel space.

Based on this work and the designed attack and threat model, an architecture and concepts, as well as technical details of mechanisms and procedures of involved components, will be developed and established. The technical solution to be developed will provide secure, reliable measurement, reporting and verification of runtime system states that can be carried out repeatedly to monitor targeted systems over a long period of time. Consequently, the result will be a complete runtime protection technology that can detect attacks on software at runtime that were previously undetectable.

The designed runtime protection technology will be instantiated in a prototype implementation to demonstrate the applicability of the solution, along with several components and tools, such as: (1.) memory measurement – to measure identified user and kernel space artifacts, implementing an effective data-collection design and anchoring the measurements to a security module; (2.) procedures to generate reference values based on reliable sources for the verification of the measured artifacts, and (3.) a reference implementation for the verification of the measured artifacts based on the collected or to be calculated reference values.

The prototype implementation will further be used to verify the initial concepts, to demonstrate performance impact to the system and to prove the successful detection of runtime attacks considered as potential threats to the system's runtime security.

#### 1.6 Contributions

This work focuses on the behavior of software and systems during their runtime and develops a runtime protection technology capable of making continuous statements about determined specific system states in a comprehensible and reliable fashion. These statements are to be attested in order to determine whether a System under Evaluation (SuE) is in a trustworthy and reliable state. In this regard, this thesis aims at making the following technical contributions:

#### (C1) Detailed security analysis of runtime attacks and threats.

A detailed analysis of the current threat and attack landscape with regard to runtime attacks will be presented in Chapter 3. This contribution is based on the results of research objective (RO1). This analysis will provide an overview of malware and derive different key properties for later classification of system runtime attacks. In addition, concrete attack techniques that are used by malware to compromise a system and hybrid attacks that are compositions of multiple attack techniques will be studied, described and classified based on the derived key

properties. Corresponding countermeasures will be investigated and presented in order to determine how resistant systems are if countermeasures are deployed. Lastly, attack methods will be developed that utilize multiple hybrid attacks to, first, avoid or disable countermeasures and then to compromise a system over a longer period of time. For this purpose, a simple model will be established that allows modeling of these attacks. Additionally, these complex attacks will build the basis for defining executable attack scenarios that will be used later to evaluate the other technical contributions of this work.

#### (C2) Novel and holistic runtime protection technology.

The main contribution of this thesis is to provide the novel and holistic runtime protection technology Dynamic Integrity Runtime Verification and Evaluation (DRIVE). This will be achieved by the combined results of the research objectives (RO1) and (RO2) and will be addressed in the Chapter 4 and 5. DRIVE will enhance established static load-time attestation concepts by enabling a granular and continuous measurement, reporting and verification of different data artifacts present in the system memory during software runtime. For this purpose, a high-level attestation concept will be developed, and a flexible architecture will be designed that supports different instantiations of DRIVE. This architecture will identify and introduce necessary systems and components that will be used to establish an instantiated software architecture describing the individual building blocks alongside corresponding procedures of operations. A deployment analysis will also be carried out to derive requirements and to identify constraints for its implementation. Subsequently, required data-structures and mechanisms for measurement, reporting and verification will be defined and described in detail. In this context, great importance will be placed on the generalization of the developed data structures and mechanisms to support a secure and reliable attestation of different types of memory data artifacts in a unified way. Finally, a security analysis based on derived attack scenarios will be carried out and discussed.

#### (C3) Implementation and evaluation of the runtime protection technology.

A prototypical implementation of DRIVE will be provided and evaluated with regard to effects on system performance and achieved security capabilities. This contribution is based on the results of research objective (RO3) and addressed in Chapter 6. First, the implementation will be realized as a Proof of Concept (PoC) that implements the designed software architecture, defines data-structures and describes corresponding mechanisms for runtime memory data attestation. This will include secure and repeatable data acquisition, integrity-verifiable report generation and reliable verification on the basis of well-known trusted references. Second, a security analysis on the basis of the defined attack scenarios will be

carried out. Therefore, the attack scenarios will be simulated and evaluated by the PoC. The results of this analysis will determine whether DRIVE is a practical and implementable solution capable of detecting concrete memory-based attacks during software runtime. Lastly, the component implementing the measurement mechanism will be evaluated regarding its effects on the system on which it is deployed. Different optimizations will also be evaluated that aim at limiting the effects of the measurement acquisition process.

#### 1.7 Outline

Chapter 2 builds the foundation of this thesis and discusses basic technical concepts that will be used in the course of this thesis. For this purpose, general concepts and mechanisms are briefly discussed which introduce and present program execution, loading processes, memory management and specific object properties of the resources used.

Chapter 3 provides a detailed security analysis of threats and attacks. First, malware is introduced and classified according to various properties. This is followed by a presentation and detailed analysis of attack techniques that can be used to break into systems or software at runtime. Existing countermeasures are discussed and examined for their effectiveness. Next, the actual threats are discussed and different attack scenarios are defined using a developed model for hybrid attack techniques.

Chapter 4 introduces a high-level concept and an architecture that allows attestation of runtime system states on a trustworthy third-party system. Subsequently, on the basis of the concept and the architecture, more precise system components are developed, and an instantiation of a software architecture is presented. Furthermore, a deployment analysis is carried out which examines the isolation of different system components and identifies architectural limitations.

Chapter 5 describes the mechanisms and procedures of the instantiated architecture in detail. For this purpose, the individual mechanisms and procedures are structured on the basis of data to be attested. The attestation mechanisms are divided into measurement, reporting and verification of memory data. In the first step, simple and commonly applicable data structures are defined, and a general transfer protocol is specified. This is followed by more complex attestation concepts, which are based on the mechanisms and data structures developed for refining them further. At the end of the chapter, a security analysis is carried out to ensure that the defined attack scenarios are covered from a conceptual point of view and also to provide conclusions and suggestions for implementation.

Chapter 6 describes the implementation of the prototype. The concrete implementation of the software components is discussed and the concepts used in the development are explained. This is illustrated by an attestation example. A security analysis is then

carried out in order to prove the effectiveness of the developed concepts on the basis of their implementation. For this purpose, certain attacks on the system are simulated, and which attacks were recognized by the implementation are analyzed. The final step is an evaluation of the prototype with regard to its performance. In particular, the measurement process is evaluated here because it has direct effects on the system to be monitored, but is not necessary for strictly operational reasons.

Chapter 7 puts the results of this work in relation to related research. The related research and the state-of-the-art technologies are first presented and described. The contributions of this work are categorized and discussed for each individual research area. In particular, the actual contributions to the current state-of-the-art approaches will be discussed.

Chapter 8 summarizes the results of this work and refers to the research questions and objectives presented in the introduction. The conclusion of this chapter presents the outlook for future work that should be considered in this area.

# Technical Background

This chapter introduces the technical principles that this work is based on. The concept of this work is deeply integrated into the operating system's basic low-level functionality and based on various principles and technologies. First, the basics of loading and executing a program are briefly described. Particular focus is put on the transition from a file-based program to an executable in-memory program which is explained for kernel and user space components. Next, different types of programs, more precisely variants of program text, are identified and described. This is essential for the conceptual work, because the variants of program text influence the loading of programs which, in turn, affects their representation in the system memory. Last, related memory management concepts are described for which an overview of memory access and protection for memory mapped segments and sections is provided. In addition to that, this chapter discusses the static and dynamic behavior of these mappings and provides a definition for predictability.

# 2.1 Program Execution Principles in Computer Architectures

The execution of every program meant to run on a computer system follows a certain method. Leaving aside the specific software components, every Central Processing Unit (CPU)-based computation relies on instructions and data present in the system's main memory. Even though different architectures come with different concrete implementations for the process, all modern architectures follow certain principles and are based on a similar organization of the data involved and on the invocation of related operations that apply computations on them.

Before the CPU starts computations, architecture-specific registers are filled with a instruction and data from the system memory. Data refers to all kinds of different structures such as constants, variables or pointers. The corresponding LOAD instruction from the Instruction Set Architecture (ISA) moves bytes from the system memory to the registers

and the STORE instruction moves the register content from the registers back to the system memory. During a typical instruction-execution cycle, an instruction is first fetched from the system memory. This instruction may cause fetching additional data (operands) that are also present in the system memory. After the instruction's execution, the result may be stored back in the system memory, c.f. [21]. This execution cycle follows a strict sequence; the CPU executes one instruction after another, unless interrupted, terminated or completed.

The set of instructions present in memory is known as the code base and the sequential execution of these instructions is managed by one specific register, referred to as the Instruction Pointer (IP). The IP points to the currently executed instruction and once the instruction has finished its execution, the IP is incremented by one and the execution cycle starts again. However, if a control flow transition instruction has been executed – i.e. a branch instruction – the IP is altered accordingly and points to the newly computed or assigned branch value. In both cases the specified instruction is executed by the CPU as described and the execution cycle continues as described until a final instruction is executed that eventually terminates the program.

# 2.2 Program Loading in Modern Operating Systems

# 2.2.1 Organization of Program Text and Data

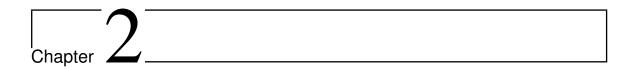

In Unix-based systems, the Executable and Linkable Format (ELF) is a standard file format defining the organizational structures of executables, shared libraries, and core dumps that act as containers for the program text and data portions of a program. Inside the ELF, different portions of the program text and data are represented by different sections. The most notable sections are (1) the .text, .init, and .plt sections, encapsulating executable instructions, (2) the .data, .rodata and .bss sections, holding initialized and uninitialized data, and (3) the .got section, a table that organizes data structures used for resolving function symbols. There are more sections in the ELF (e.g., programand section headers, and procedure- and symbol resolution tables). A comprehensive overview is given in [22]. Figure 2.1 shows an ELF to Virtual Address Space (VAS) user space mapping example. As shown, multiple related sections from the ELF are organized in a single segment. This relation is specified in the Section to Segment mapping in the ELF header and can be different for each ELF.

#### 2.2.2 Loading Processes of Programs

Before instructions can be executed by the CPU, the required program text must fully reside in the system memory. Depending on the actual program, different loaders are responsible for the loading process. There is the Bootloader, the Kernel Module Loader

**Figure 2.1** – ELF to VAS Mapping demonstrating Section to Segment Mappings for a 32-bit System.

and the User Space Process Loader for ELF. The result, after all loading mechanisms have been executed, is shown in Figure 2.1 and is described in the following for each bootloader.

System Bootloader and Kernel Setup The Bootloader instructs the CPU to load the OS Kernel into the system memory at a fixed location. From this point onward, the Kernel takes complete control over the memory management. If the Memory Management Unit (MMU) is present, the Kernel initializes it and sets up internal structures to organize the mappings between the physical and virtual memory; the managing structure is referred to as the *page table* [23]. Most importantly, in this process the virtual memory is separated into kernel space and user space. Afterwards, the Kernel continues with its execution until an Loadable Kernel Module (LKM) needs to be loaded. If there are no LKMs, control is transferred to the user space process loader and management system, conducted for instance by *init*, *systemd* or *upstart* on Linux-based OS.

**Kernel Module Loader** The Kernel Module Loader (KML) loads the requested LKM ELF program text into memory and transforms the LKM into a ready-to-run state. During this process, dependencies between different LKMs are resolved.

More precisely, the KML (1) inspects every unresolved symbol, either referencing procedures or data from the LKM itself, the Kernel or other LKMs; (2) resolves the symbol by determining the targeted Virtual Memory Address (VMA); and (3) patches the determined target VMA code pointer directly into the program text in LKMs'.text segment present in the system memory. After all transformations are applied, the LKM is in a ready-to-run state and can be invoked and executed as intended.

**User Space Process Loader** After the OS kernel has finished its loading process, the control is redirected to user space process management programs. Every user space process is organized in the same way: It has the same view of the available system resources, i.e. the VAS, as depicted in Figure 2.1. The layout and size of the VAS is identical for every process. The typical size for the 32-Bit VAS is 4 GB with two segmentations:

- User space 3 GB (0x0000000 0xBFFFFFFF)

- Kernel space 1 GB (0xC0000000 0xFFFFFFFF)

By contrast, 64-bit systems usually implement an address width of 48 bits, resulting in 256TB VAS:

- User space 128 TB (0x00000000000000 0x00007FFFFFFFFFF)

- Kernel space 128 TB (0xffff8000000000 0xfffffffffffffff)

The actual process-loader program invoked in Linux systems is implemented by ld-linux.so (LD) [24]. Similar to the KML, LD loads the program into the system memory and executes the symbol resolution and relocation process [25], where appropriate (c.f. Section 2.3). Usually, programs depend on external libraries which are, in turn, again programs consisting of program text and data encapsulated in ELF¹. Therefore, LD also loads all referenced shared libraries into the process memory, before the symbol resolution and relocation phase is performed. The symbol resolution and relocation are also executed for every shared library, as dependencies between different shared libraries occur very frequently. After the dependency loading, function resolution and relocation phase of LD has been successfully completed, the final process image is in a ready-to-run state. In a final step, LD delegates the execution to the loaded program by calling its main() routine. From that point onward, the program is available as a process in the system. One process image of a loaded program is depicted in Figure 2.1, including the memory layout of an LD loaded library.

Although shared libraries are programs, they cannot be executed or invoked directly; they lack a starting routine.

# 2.3 Program Text Variants

Program text is categorized into two variants that influence the loading process during the transformation into a ready-to-run state.

- 1. Position Independent Code (PIC) uses relative addressing and can thus be executed from arbitrary memory addresses.

- 2. Relocatable Code (RCC) depends on definite absolute memory addresses that must be resolved by the linker or loader prior to RCC's execution.

Position Independent means that the source code was compiled in a special way by eliminating the use of direct memory addresses within the program text. Necessary memory-based address access (target addresses) are resolved in PIC with a Global Offset Table (GOT) [25, 26] mapped to a specific .got memory region.

In contrast to PIC, RCC relies on direct memory addresses inside the program text for function calling. Inside the program text, certain placeholders exist which are replaced during the relocation process by calculating relative or absolute target addresses. These replacements take place during the link or the load time. Both variants have certain benefits and effects on the DRIVE concept which will be subsequently enlarged upon.

#### 2.3.1 Relocatable Code

RCC is the standard mechanism for generating program text for user space programs, the Kernel and LKMs. Necessary relocations that rely on fixed memory addresses are resolved either during the linking phase or during the load-time with the help of the dynamic runtime loader [24]. More precisely, program text in user space and the OS kernel is at least deferred until the link-time because it depends on a fixed load address, which means that relocation can happen earliest during the linking phase [25].

For the link time relocated program text, the instructions already contain the concrete target addresses for all symbols or use relative addressing. This means the .text segment's program text within the ELF is identical to the program text in the memory segment. A relocation after the linking phase is therefore not necessary. In other words, although the link time relocated program text is based on relocatable code, it behaves more like PIC during loading and execution, explained in the next Section 2.3.2.

In contrast to this, there are LKMs that cannot be relocated during link time since they depend on dynamic addresses only available during runtime. Instead, the RCC ELF contains a specific symbol table and the program text uses placeholders for all referenced symbol addresses. During the loading process the loader analyses this symbol table, resolves the target addresses of the symbols and patches the program text placeholders accordingly with resolved concrete target addresses. In case of LKM loading, symbols

from both the Kernel and other LKMs are resolved and taken into consideration during the relocation process.

Although RCC plays a negligible role for shared libraries today, the process of symbol resolution and program text patching is similar to the one described for LKMs. Instead of the LKM loader, the user space process loader 1d is responsible for relocation. In this case, symbols from other libraries are the main target during the symbol resolution process.

# 2.3.2 Position Independent Code

Generating PIC for shared libraries is the default behavior in any modern Linux system; all shared libraries in Linux are PIC.

During the loading process of PIC, the program text remains unchanged and identical to its counterpart in the ELF. As mentioned, the same principle applies for link time RCC. The main benefit of this is the possibility to share memory mapped content between multiple processes<sup>2</sup>. As long as a page-mapped portion remains unchanged it is shared with other processes in the system, and thus resides only one time in physical memory. Considering that many resources, such as libraries like for instance glibc and libld are shared between all processes, this deduplication of resources saves a considerable amount of physical memory.

Recently, so called Position Independent Executables (PIEs) become more relevant and are used in many current Linux distributions, replacing the link time RCC ELF. Regarding the resource sharing and behavior PIE is equal to link time RCC and PIC. Accordingly, for the rest of this work, the term PIC is also used to denote PIE if not indicated otherwise.

In contrast to link time RCC, PIC benefits hugely from Address Space Layout Randomization (ASLR), since it does not rely on fixed addresses and thus renders possible vulnerability exploitation harder, because fully resolved memory addresses are often required to conduct certain attacks. Additionally, PIC also facilitates the dynamic loading of shared libraries during runtime, which is used by many applications with the assistance of the <code>dlopen</code> system call. From the perspective of DRIVE, link time RCC and PIC are equal. This means the measurement and verification of corresponding <code>.text</code> segments are fully supported.

# 2.3.3 Program Text Distribution Analysis

To provide a better overview of the program text variants and which variants are used, three different distributions (Ubuntu, Debian and Fedora) for three different architectures (X86, X86\_64, ARM64) were analyzed to determine the distribution of PIC, PIE and link-time RCC program text. In order to determine if PIE was used, the Linux tool

<sup>&</sup>lt;sup>2</sup> This sharing, the main advantage of PIC, is not necessary for LKMs since one LKM may only be available as a single instance in kernel space.

| Operating System      | Architecture | All | PIC        | $RCC_{load}$ | Canaries  |

|-----------------------|--------------|-----|------------|--------------|-----------|

| Fedora Cloud (21)     | X86          | 921 | 921 (100%) | 0 (0%)       | 395 (43%) |

| Debian (wheezy)       | X86_64       | 701 | 701 (100%) | 0 (0%)       | 174 (25%) |

| Debian (wheezy)       | X86          | 705 | 705 (100%) | 0 (0%)       | 193 (27%) |

| Ubuntu (vivid server) | X86_64       | 892 | 892 (100%) | 0 (0%)       | 480 (54%) |

| Ubuntu (vivid server) | ARM64        | 883 | 883 (100%) | 0 (0%)       | 461 (52%) |

| Ubuntu (vivid server) | X86          | 891 | 891 (100%) | 0 (0%)       | 482 (54%) |

**Table 2.1** – Program Text Variant Analysis for Shared Libraries.

Table 2.2 – Program Text Variant Analysis for Programs.

| Operating System      | Architecture | All | $RCC_{link}$ | PIE       | Canaries  |

|-----------------------|--------------|-----|--------------|-----------|-----------|

| Fedora Cloud (21)     | X86          | 687 | 482 (70%)    | 205 (30%) | 590 (86%) |

| Debian (wheezy)       | X86_64       | 650 | 576 (89%)    | 74 (11%)  | 406 (63%) |

| Debian (wheezy)       | X86          | 676 | 577 (85%)    | 99 (15%)  | 416 (62%) |

| Ubuntu (vivid server) | X86_64       | 808 | 585 (72%)    | 223 (28%) | 704 (87%) |

| Ubuntu (vivid server) | ARM64        | 777 | 558 (72%)    | 219 (29%) | 655 (84%) |

| Ubuntu (vivid server) | X86          | 807 | 584 (72%)    | 223 (28%) | 705 (87%) |

hardening-check was run. On top of that, the distinction between PIC and RCC was made on the basis of available relocation tables or available Procedure Linkage Table (PLT) code<sup>3</sup>.

As shown in Table 2.1, all shared libraries use exclusively PIC. Additionally, the analysis confirmed that most executable ELF files still use link-time RCC relocation. However, PIEs were found in all analyzed systems, see Table 2.2. In addition to that, the last column in each table indicates whether stack canaries were used. This will be discussed in greater detail in Section 3.2.4.

Regarding kernel space, load-time relocated RCC still plays a major role for LKM. All LKMs analyzed use load-time RCC and are thus relocated during initial loading. The Kernel images are, as expected, all statically linked.

#### 2.3.4 Global Offset Table

Both PIC and link time RCC in user space are usually paired with a mechanism called lazy-binding [24], implementing an on-demand function symbol resolution and relocation process. This means that whenever a symbol is used for the first time during execution it is resolved by a special component of the runtime loader and afterwards invoked.

Technically, the symbol resolution involves the maintenance<sup>4</sup> of a table known as the Global Offset Table (GOT) (.got). The symbol resolution mechanism is rather complex, because it involves trampoline jumps to symbol resolution functions of the loader on first

https://stackoverflow.com/questions/1340402/how-can-i-tell-with-something-like-objdump-if-an-object-file-has-been-built-wi

Managed by the Procedure Linkage Table .plt as part of the .text segment.